現(xiàn)在看到手機(jī)發(fā)布會(huì),很多廠(chǎng)商在介紹處理器的時(shí)候總會(huì)蹦出“FinFet工藝制造”之類(lèi)的名詞,那到底什么是FinFET工藝,到底有什么優(yōu)勢(shì)讓國(guó)際大廠(chǎng)趨之若鷲?

晶體管

FinFET工藝的概念

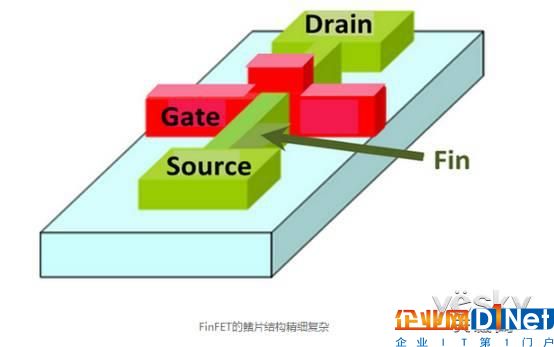

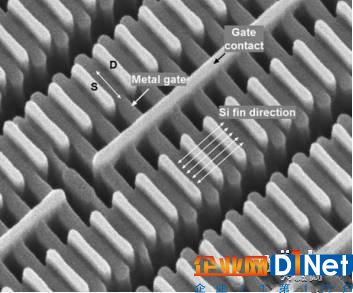

FinFET稱(chēng)為鰭式場(chǎng)效應(yīng)晶體管(Fin Field-Effect Transistor),是由美籍華人科學(xué)家胡正明教授提出的,其中的Fin在構(gòu)造上與魚(yú)鰭非常相似,所以稱(chēng)為“鰭式”,而FET的全名是“場(chǎng)效電晶體” 。

FinFET是一種新的互補(bǔ)式金屬氧半導(dǎo)體(CMOS)晶體管,源自于傳統(tǒng)標(biāo)準(zhǔn)的晶體管—“場(chǎng)效晶體管”的一項(xiàng)創(chuàng)新設(shè)計(jì)。

立體式Fin

傳統(tǒng)晶體管結(jié)構(gòu)是平面的,所以只能在閘門(mén)的一側(cè)控制電路的接通與斷開(kāi)。但是在FinFET架構(gòu)中,閘門(mén)被設(shè)計(jì)成類(lèi)似魚(yú)鰭的叉狀3D架構(gòu),可于電路的兩側(cè)控制電路的接通與斷開(kāi)。這種叉狀3D架構(gòu)不僅能改善電路控制和減少漏電流,同時(shí)讓晶體管的閘長(zhǎng)大幅度縮減。

采用FinFET工藝的第三代酷睿處理器

最早使用FinFET工藝的是英特爾,他們?cè)?2納米的第三代酷睿處理器上使用FinFET工藝,隨后各大半導(dǎo)體廠(chǎng)商也開(kāi)始轉(zhuǎn)進(jìn)到FinFET工藝之中,其中包括了臺(tái)積電16nm、10nm、三星14nm、10nm以及格羅方德的14nm。

不過(guò)FinFET工藝的極限是7nm制程,第一代的7nm工藝還將會(huì)繼續(xù)使用FinFET工藝,但是接下來(lái)就需要依賴(lài)極紫外光刻機(jī)了。

FinFET工藝的制造

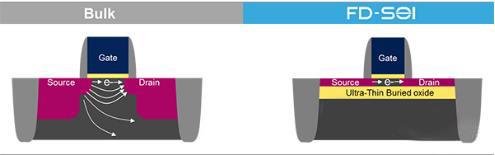

前面提到的FinFET可以理解為立體的晶體管,傳統(tǒng)平面的晶體管所采用的是FD-SOI工藝。雖然這幾年的FinFET工藝占據(jù)了大多數(shù)人的視線(xiàn),但是FD-SOI工藝依然非常重要。

如果要是FinFET工藝核FD-SOI達(dá)到相同性能,F(xiàn)D-SOI工藝在制造過(guò)程中相對(duì)簡(jiǎn)單,但是SOI基片價(jià)格稍貴,而FinFET工藝雖然制造過(guò)程更為復(fù)雜,但是由于基片價(jià)格便宜,讓兩者的實(shí)際制造成本相差不大。

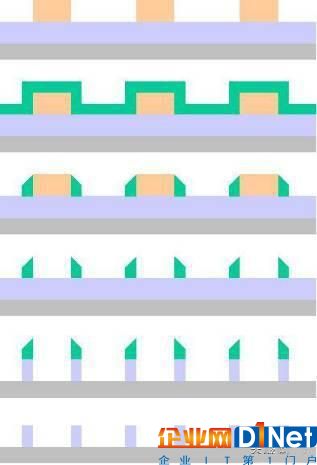

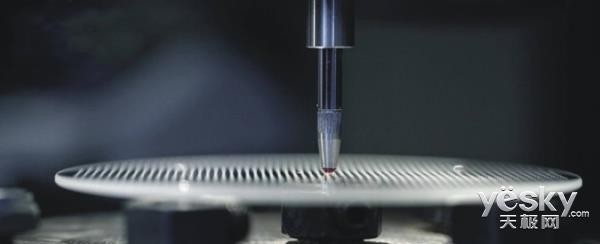

前面提到FinFET的制造工藝是非常復(fù)雜的,Intel的Mark Bohl在2016年的一個(gè)訪(fǎng)談中聊到了FinFET技術(shù),并提到Intel將會(huì)繼續(xù)使用SADP (Self-Aligned Double Patterning)工藝。

其中的Double Patterning是目前主流的FinFET制造工藝。它的原理就是先pattern一批80nm精度的圖樣,然后再交錯(cuò)Pattern一批80nm精度的圖樣;在兩次光刻之后,就可以將精度提升到40nm。

英特爾的做法就是先用普通精度的光刻可出一堆“架子”,然后在架子上沉淀一層很薄的硅,再選擇性的使用把多余的材料弄走,剩下立著的就是超薄的Fin了。準(zhǔn)確點(diǎn)來(lái)說(shuō),這個(gè)Fin不是刻出來(lái)的,而是長(zhǎng)出來(lái)的。

FinFET工藝的改良

FinFET工藝實(shí)質(zhì)上就是再原油的基礎(chǔ)上增加了一個(gè)柵極,這樣可以讓尺寸很小的晶體管減少漏電。因?yàn)榇蟛糠值穆╇娛莵?lái)自于溝道下方的流通區(qū)域,也就是短溝道效應(yīng)。

那要如何解決掉短溝道效應(yīng)呢?

就有人開(kāi)始想:既然電子是在溝道中運(yùn)動(dòng),物理模型需要這片區(qū)域來(lái)平衡電荷,所以就有了溝道下方的耗盡層。但在短溝道器件里面,把耗盡層和溝道放在一起,等著漏電流白白地流過(guò)去。

FD-SOI工藝

于是IBM研究人員開(kāi)了一個(gè)腦洞:把這部分硅換成絕緣層,這樣溝道就和耗盡層分開(kāi)了。因?yàn)殡娮觼?lái)源于兩極,但是兩極和耗盡層之間被絕緣層隔開(kāi),這樣除了溝道外,其他地方就不會(huì)產(chǎn)生漏電了,這就是SOI工藝。

SOI工藝雖然沒(méi)能成為主流,但是依然有很多制造廠(chǎng)在搞,格羅方德和意法半導(dǎo)體就有FD-SOI工藝產(chǎn)品。

英特爾可不這么想:既然要在將耗盡層的硅換成絕緣的氧化物,拿為什么還要放一層沒(méi)用的硅在下面,直接在氧化層底下弄一個(gè)柵極,兩邊夾著溝道,不是更爽?

現(xiàn)在英特爾還“貪心不足”,于是又想了一個(gè)改進(jìn)方法:那就是把硅弄出來(lái),周?chē)袢髦我粯影辖^緣層,外面再放上柵極,就有了FinFET工藝。

FinFET工藝的未來(lái)

技術(shù)節(jié)點(diǎn)是衡量半導(dǎo)體技術(shù)的重要標(biāo)準(zhǔn),但并不是絕對(duì)的。臺(tái)積電也好、三星半導(dǎo)體也罷,最掙錢(qián)的并不是最先進(jìn)的技術(shù)工藝,而是相對(duì)成熟的技術(shù)節(jié)點(diǎn)。

對(duì)于IC設(shè)計(jì)廠(chǎng)商來(lái)說(shuō),成本、性能、需求多方面達(dá)到平衡的方案和技術(shù)節(jié)點(diǎn)是最重要的,企業(yè)不是慈善家,它也需要考慮盈利的問(wèn)題,很多芯片在產(chǎn)品性能足夠的情況下,選擇最合適的制造工藝,可以提升市場(chǎng)競(jìng)爭(zhēng)力,擴(kuò)大市場(chǎng)占有率。

臺(tái)積電在去年的IEDM上發(fā)布7nm技術(shù)節(jié)點(diǎn)的晶體管樣品,雖然說(shuō)臺(tái)積電的7nm工藝在技術(shù)節(jié)點(diǎn)與英特爾的10nm非常相似,但臺(tái)積電已經(jīng)大有趕超英特爾之勢(shì)。

7nm制程的FinFET工藝最快要到明年才能面世,7nm也是FinFET工藝的極限,再往下的節(jié)點(diǎn)只能看EUV光刻機(jī)。

及時(shí)披露上市公司公告,提供公告報(bào)紙版面信息,權(quán)威的“中證十條”新聞,對(duì)重大上市公司公告進(jìn)行解讀。

京公網(wǎng)安備 11010502049343號(hào)

京公網(wǎng)安備 11010502049343號(hào)