中國(guó)半導(dǎo)體IP行業(yè)未來(lái)發(fā)展趨勢(shì)

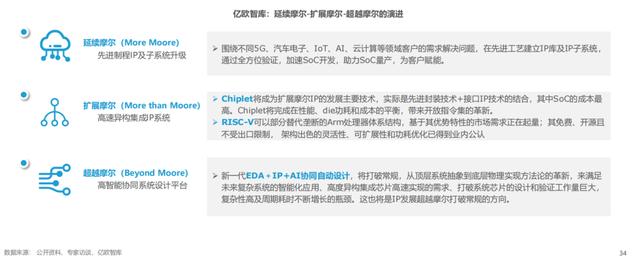

后摩爾時(shí)代半導(dǎo)體IP發(fā)展趨勢(shì)和方向:延續(xù)摩爾、擴(kuò)展摩爾、超越摩爾

后摩爾時(shí)代,IP發(fā)展趨勢(shì)將分為三個(gè)階段:延續(xù)摩爾、擴(kuò)展摩爾和超越摩爾。

延續(xù)摩爾主要是根據(jù)客戶需求解決問題,加速SoC開發(fā);擴(kuò)展摩爾將采用Chiplet技術(shù)實(shí)現(xiàn)性能、功耗和成本的平衡,并加速開放指令集革新;超越摩爾將結(jié)合先進(jìn)工藝、先進(jìn)封裝、智能協(xié)同自動(dòng)設(shè)計(jì)等技術(shù)作為撬動(dòng)整個(gè)芯片產(chǎn)業(yè)需求的支點(diǎn),打破常規(guī),從頂層系統(tǒng)抽象到底層物理實(shí)現(xiàn)方法論的革新。

延續(xù)摩爾:新工藝節(jié)點(diǎn)技術(shù)的誕生打破技術(shù)瓶頸

晶體管尺寸縮小時(shí),短溝道效應(yīng)顯著,柵極對(duì)晶體管開關(guān)狀態(tài)的控制力不足,漏電流難以控制。晶體管微縮受到進(jìn)一步障礙,傳統(tǒng)的平面晶體管結(jié)構(gòu)與體硅工藝技術(shù)無(wú)法進(jìn)一步突破,持續(xù)數(shù)十年的摩爾定律有失效的可能性。

為繼續(xù)延續(xù)摩爾定律的演進(jìn),集成電路新工藝節(jié)點(diǎn)技術(shù)FinFET、GAA和FD-SOI的誕生,打破了技術(shù)瓶頸。

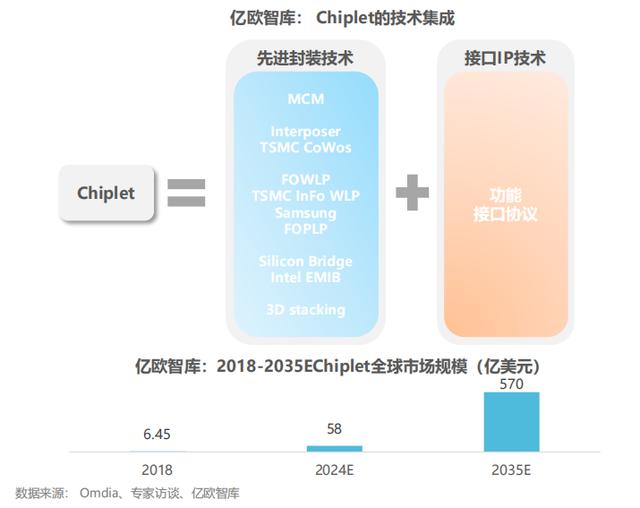

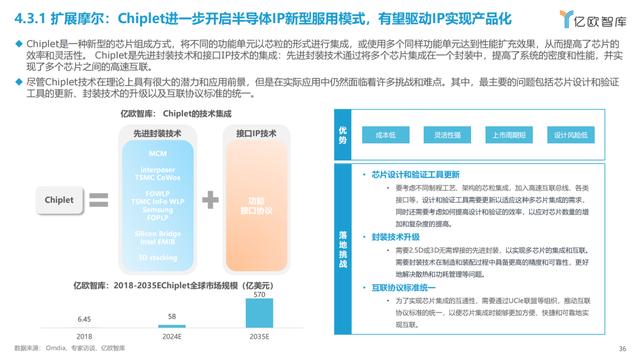

擴(kuò)展摩爾:Chiplet進(jìn)一步開啟半導(dǎo)體IP新型服用模式,有望驅(qū)動(dòng)IP實(shí)現(xiàn)產(chǎn)品化

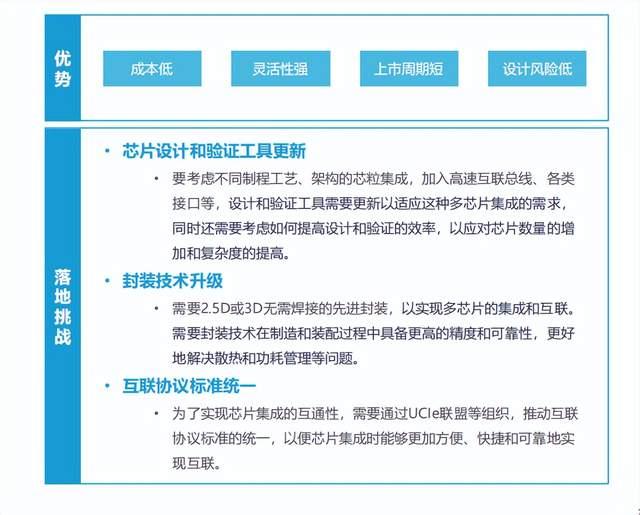

Chiplet是一種新型的芯片組成方式,將不同的功能單元以芯粒的形式進(jìn)行集成,或使用多個(gè)同樣功能單元達(dá)到性能擴(kuò)充效果,從而提高了芯片的效率和靈活性。Chiplet是先進(jìn)封裝技術(shù)和接口IP技術(shù)的集成:先進(jìn)封裝技術(shù)通過(guò)將多個(gè)芯片集成在一個(gè)封裝中,提高了系統(tǒng)的密度和性能,并實(shí)現(xiàn)了多個(gè)芯片之間的高速互聯(lián)。

盡管Chiplet技術(shù)在理論上具有很大的潛力和應(yīng)用前景,但是在實(shí)際應(yīng)用中仍然面臨著許多挑戰(zhàn)和難點(diǎn)。其中,最主要的問題包括芯片設(shè)計(jì)和驗(yàn)證工具的更新、封裝技術(shù)的升級(jí)以及互聯(lián)協(xié)議標(biāo)準(zhǔn)的統(tǒng)一。

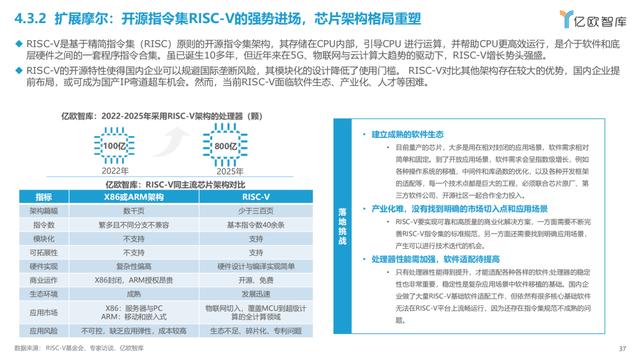

擴(kuò)展摩爾:開源指令集RISC-V的強(qiáng)勢(shì)進(jìn)場(chǎng),芯片架構(gòu)格局重塑

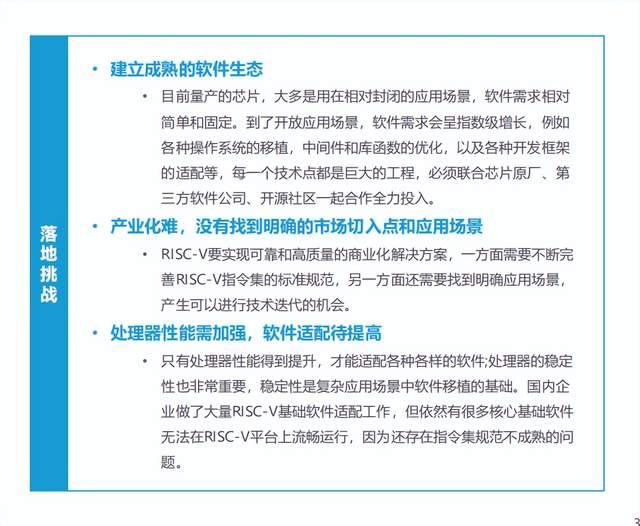

RISC-V是基于精簡(jiǎn)指令集(RISC)原則的開源指令集架構(gòu),其存儲(chǔ)在CPU內(nèi)部,引導(dǎo)CPU 進(jìn)行運(yùn)算,并幫助CPU更高效運(yùn)行,是介于軟件和底層硬件之間的一套程序指令合集。雖已誕生10多年,但近年來(lái)在5G、物聯(lián)網(wǎng)與云計(jì)算大趨勢(shì)的驅(qū)動(dòng)下,RISC-V增長(zhǎng)勢(shì)頭強(qiáng)盛。

RISC-V的開源特性使得國(guó)內(nèi)企業(yè)可以規(guī)避國(guó)際壟斷風(fēng)險(xiǎn),其模塊化的設(shè)計(jì)降低了使用門檻。RISC-V對(duì)比其他架構(gòu)存在較大的優(yōu)勢(shì),國(guó)內(nèi)企業(yè)提前布局,或可成為國(guó)產(chǎn)IP彎道超車機(jī)會(huì)。然而,當(dāng)前RISC-V面臨軟件生態(tài)、產(chǎn)業(yè)化、人才等困難。

超越摩爾:新一代協(xié)同自動(dòng)設(shè)計(jì)實(shí)現(xiàn)方法論革新

隨著技術(shù)的不斷發(fā)展,芯片的設(shè)計(jì)和制造變得越來(lái)越復(fù)雜,要求IP必須具備更高的適配性和達(dá)成智能化與自動(dòng)化。

新一代EDA+IP+AI協(xié)同自動(dòng)設(shè)計(jì),將打破常規(guī)從頂層系統(tǒng)抽象到底層物理實(shí)現(xiàn)方法論的革新、滿足高度異構(gòu)集成芯片實(shí)現(xiàn)需求、突破芯片設(shè)計(jì)、 驗(yàn)證工作瓶頸。未來(lái)IP將結(jié)合先進(jìn)工藝、先進(jìn)封裝、智能協(xié)同自動(dòng)設(shè)計(jì)作為撬動(dòng)整個(gè)芯片產(chǎn)業(yè)需求的支點(diǎn)。

以下是報(bào)告節(jié)選正文內(nèi)容:

京公網(wǎng)安備 11010502049343號(hào)

京公網(wǎng)安備 11010502049343號(hào)