如題,先從大廠說起。目前芯片廠商有三類:IDM、Fabless、Foundry。

IDM(集成器件制造商)指 Intel、IBM、三星這種擁有自己的晶圓廠,集芯片設計、制造、封裝、測試、投向消費者市場五個環節的廠商,一般還擁有下游整機生產。

Fabless(無廠半導體公司)則是指有能力設計芯片架構,但本身無廠,需要找代工廠代為生產的廠商,知名的有 ARM、NVIDIA、高通、蘋果和華為。

Foundry(代工廠)則指臺積電和 GlobalFoundries,擁有工藝技術代工生產別家設計的芯片的廠商。我們常見到三星有自己研發的獵戶座芯片,同時也會代工蘋果 A 系列和高通驍龍的芯片系列,而臺積電無自家芯片,主要接單替蘋果和華為代工生產。

制程

在描述手機芯片性能的時候,消費者常聽到的就是 22nm、14nm、10nm 這些數值,這是什么?

這是芯片市場上,一款芯片制程工藝的具體數值是手機性能關鍵的指標。制程工藝的每一次提升,帶來的都是性能的增強和功耗的降低,而每一款旗艦手機的發布,常常與芯片性能的突破離不開關系。

驍龍 835 用上了更先進的 10nm 制程, 在集成了超過 30 億個晶體管的情況下,體積比驍龍 820 還要小了 35%,整體功耗降低了 40%,性能卻大漲 27%。

深入來說,這幾十納米怎么計算出來的?我們從芯片的組成單位晶體管說起。

得益于摩爾定律的預測,走到今天,比拇指還小的芯片里集成了上億個晶體管。蘋果 A10 Fusion 芯片上,用的是臺積電 16nm 的制造工藝,集成了大約 33 億個晶體管。

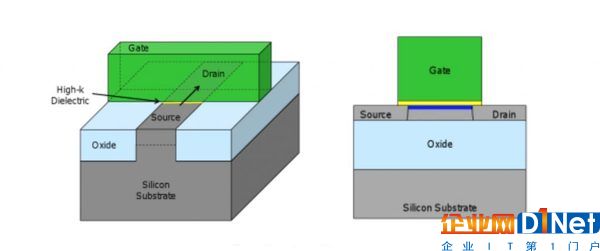

而一個晶體管結構大致如下:

圖中的晶體管結構中,電流從 Source(源極)流入 Drain(漏級),Gate(柵極)相當于閘門,主要負責控制兩端源極和漏級的通斷。電流會損耗,而柵極的寬度則決定了電流通過時的損耗,表現出來就是手機常見的發熱和功耗,寬度越窄,功耗越低。而柵極的最小寬度(柵長),就是 XX nm工藝中的數值。

對于芯片制造商而言,主要就要不斷升級技術,力求柵極寬度越窄越好。不過當寬度逼近 20nm 時,柵極對電流控制能力急劇下降,會出現“電流泄露”問題。為了在 CPU 上集成更多的晶體管,二氧化硅絕緣層會變得更薄,容易導致電流泄漏。

一方面,電流泄露將直接增加芯片的功耗,為晶體管帶來額外的發熱量;另一方面,電流泄露導致電路錯誤,信號模糊。為了解決信號模糊問題,芯片又不得不提高核心電壓,功耗增加,陷入死循環。

因而,漏電率如果不能降低,CPU 整體性能和功耗控制將十分不理想。這段時間臺積電產能跟不上很大原因就是用上更高制程時遭遇了漏電問題。

還有一個難題,同樣是目前 10nm 工藝芯片在量產遇到的。

當晶體管的尺寸縮小到一定程度(業內認為小于 10nm)時會產生量子效應,這時晶體管的特性將很難控制,芯片的生產難度就會成倍增長。驍龍 835 出貨時間推遲,X30 遙遙無期主要原因可能是要攻克良品率的難關。

另外,驍龍 835 用上了 10nm 的制程工藝,設計制造成本相比 14nm 工藝增加接近 5 成。大廠需要持續而巨大的資金投入到 10nm 芯片量產的必經之路。

就目前階段,三星已經嘗試向當前的工藝路線圖中添加 8nm 和 6nm 工藝技術,臺積電方面則繼續提供 16nm FinFET 技術的芯片,開始著力 10nm 工藝的同時,預計今年能夠樣產 7nm 工藝制程的芯片。

FinFET

除了制程,還有工藝技術。

在這一代驍龍 835 上,高通選擇了和三星合作,使用三星最新的 10nm FinFET 工藝制造。同樣,三星自家的下一代旗艦獵戶座 8895 用的也是用此工藝。

FinFET 是什么?

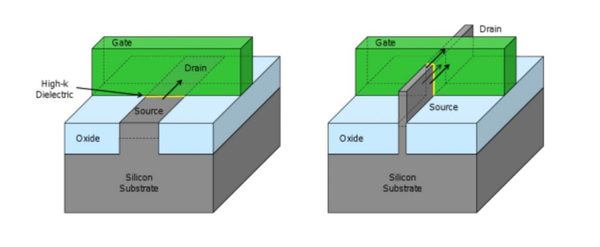

業界主流芯片還停留在 20/22nm 工藝節點上的時候,Intel 就率先引入了 3D FinFET 這種技術。后來三星和臺積電在 14/16nm 節點上也大范圍用上了類似的 FinFET 技術。下面我們統稱為 FinFET。

FinFET(Fin Field-Effect Transistor)稱為鰭式場效應晶體管,是一種新的晶體管,稱為 CMOS。具體一點就是把芯片內部平面的結構變成了3D,把柵極形狀改制,增大接觸面積,減少柵極寬度的同時降低漏電率,而晶體管空間利用率大大增加。

因為優勢明顯,目前已經被大規模應用到手機芯片上。

經歷了 14/16nm 工藝節點后,FinFET 也歷經升級,但這種升級是存在瓶頸的。目前,大廠們正研究新的 FD-SOI(全耗盡絕緣體硅)工藝、硅光子技術、3D 堆疊技術等,斥資尋求技術突破,為日后 7nm、甚至 5nm 工藝領先布局。

LPE/LPP/LPC/LPU 又是什么?

在工藝分類上,芯片主要分兩大類:

HP(High Performance):主打高性能應用范疇;

LP(Low Power):主打低功耗應用范疇。

滿足不同客戶需求,HP 內部再細分 HPL、HPC、HPC+、HP 和 HPM 五種。

HP 和 LP 之間最重要區別就在性能和漏電率上,HP 在主打性能,漏電率能夠控制在很低水平,芯片成本高;LP 則更適合中低端處理器使用,因為成本低。

所以,芯片除了在制程上尋求突破,工藝上也會逐步升級。

2014 年底,三星宣布了世界首個 14nm FinFET 3D 晶體管進入量產,標志著半導體晶體管進入 3D 時代。發展到今天,三星擁有了四代 14nm 工藝,第一代是蘋果 A9 上面的 FinFET LPE(Low Power Early),第二代則是用在獵戶座 8890、驍龍 820 和驍龍 625 上面的 FinFET LPP(Low Power Plus)。第三代是 FinFET LPC,第四代則是目前的 FinFET LPU。至于 10nm 工藝,三星則更新到了第三代(LPE/LPP/LPC)。

目前為止,三星已經將 70000 多顆第一代 LPE(低功耗早期)硅晶片交付給客戶。三星自家的獵戶座 8895,以及高通的驍龍 835,都采用這種工藝制造,而 10nm 第二代 LPP 版和第三代 LPU 版將分別在年底和明年進入批量生產。

不知不覺,手機芯片市場上已經進入了 10nm、7nm 處理器的白熱化競爭階段,而 14/16nm 制程的爭奪也不過是一兩年前的事。

之前有人懷疑摩爾定律在今天是否還適用,就芯片的進化速度和技術儲備來看,不是技術能力達不到,而是廠商們的競爭程度未必能逼迫它們全速前進。

京公網安備 11010502049343號

京公網安備 11010502049343號