硅光時代臨近,芯片集成度有望大幅提升

近年來,隨著物聯網、大數據等應用的快速發展,全球數據流量呈快速增長態勢,對傳輸的需求也逐漸提升。目前,傳統光模塊主要利用III-V族半導體芯片、電路芯片、光學組件等器件封裝而成,本質上屬于“電互聯”范疇。隨著晶體管加工尺寸逐漸縮小,電互聯將逐漸面臨傳輸瓶頸。目前,對于傳統的三五族半導體光芯片,25Gbps已接近傳輸速率的瓶頸,進一步提升速率需要采用PAM4等技術。隨著高速光模塊在數據中心的大量運用,傳統III-V族半導體的光芯片將面臨并行傳輸、三五族磊晶成本高昂等問題。在此背景下,硅光子技術應運而生,成為III-V族半導體之外的一大選擇。

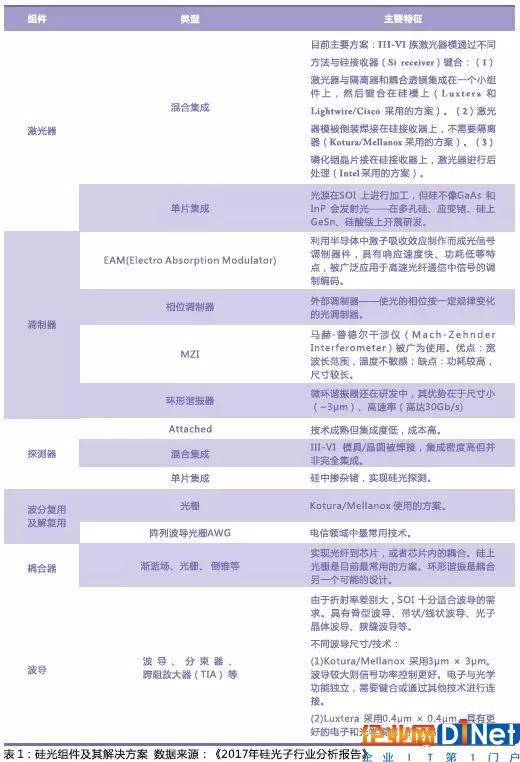

在硅光子技術中,芯片的概念由原先的激光器芯片延伸至集成芯片。從結構上看,硅光芯片包括光源、調制器、波導、探測器等有源芯片及源芯片。硅光芯片將多個光器件集成在同一硅基襯底上,一改以往器件分立的局面,芯片集中度大幅提升。硅光子技術主要有以下三大優勢:

(1)集成度高。硅光子技術以硅作為集成芯片的襯底。硅基材料成本低且延展性好,可以利用成熟的硅CMOS工藝制作光器件。與傳統方案相比,硅光子技術具有更高的集成度及更多的嵌入式功能,有利于提升芯片的集成度。

(2)成本下降潛力大。在光器件和光模塊中,光芯片的成本占比較高。傳統的GaAs/InP襯底因晶圓材料生長受限,生產成本較高。近年來,隨著傳輸速率的進一步提升,需要更大的三五族晶圓,芯片的成本支出將進一步提升。與三五族半導體相比,硅基材料成本較低且可以大尺寸制造,芯片成本得以大幅降低。

(3)波導傳輸性能優異。硅的禁帶寬度為1.12eV,對應的光波長為1.1μm。因此,硅對于1.1—1.6μm的通信波段(典型波長1.31μm/1.55μm)是透明的,具有優異的波導傳輸特性。此外,硅的折射率高達3.42,與二氧化硅可形成較大的折射率差,確保硅波導可以具有較小的波導彎曲半徑。

硅光技術持續發展,技術上不斷取得突破

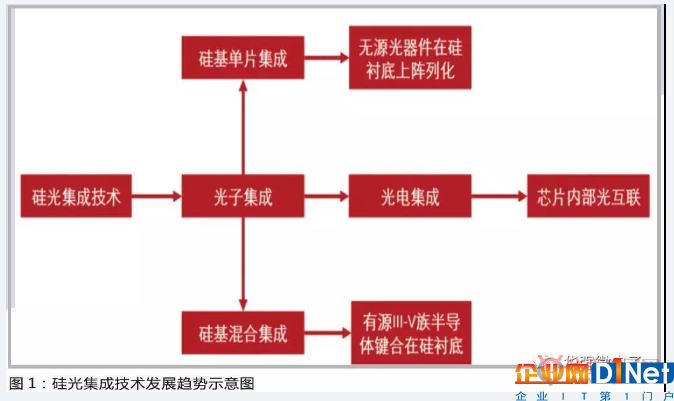

從發展歷程看,硅光集成技術將遵循由光子集成→光電集成的發展過程,待技術成熟后指向芯片內部光互聯。目前,通信領域的硅光模塊屬于光子集成范疇,從制造工藝看可分為兩類:單片集成與混合集成。

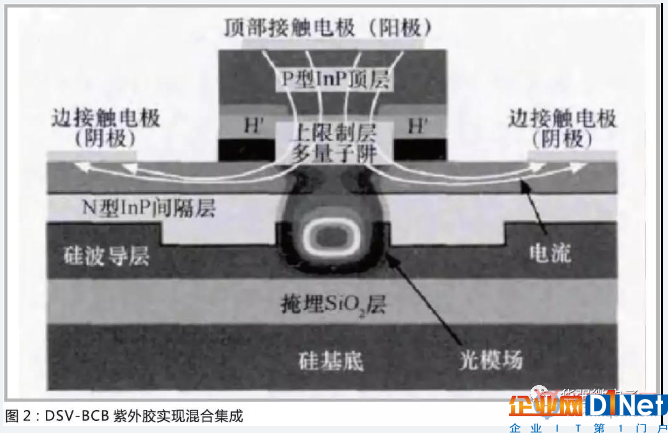

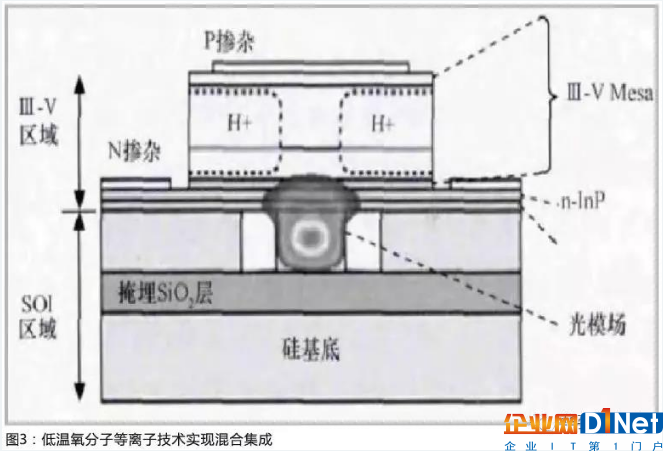

單片集成主要利用傳統的CMOS工藝,在硅晶圓上集成多個光器件。不過,硅的發光效率較低,無法作為光源,成為單片集成的瓶頸。一個折中的方法是:無源光器件在硅襯底上陣列化,光源采用III-V族半導體,混合集成技術應運而生。混合集成需要將III-V族半導體激光器鍵合在硅襯底上。鍵合技術包括利用DSV-BCB紫外膠鍵合,以及運用低溫氧分子等離子鍵合等。

在硅光集成領域,Intel是耕耘最早、技術最為完善的廠商。其中,2004年至2010年是Intel的技術突破期,2010年至2016年是商用準備期。大量的研發費用投入為2016年的硅光模塊商用奠定了堅實的基礎。對于Intel而言,未來計算機芯片的內部光互聯是其長遠目標,在通信領域的硅光模塊商用可謂初次試水。即便如此,Intel的硅光模塊對于傳統三五族半導體光模塊依舊形成了不小的沖擊。

目前,已量產的硅光模塊,基于硅襯底的混合集成是主要方式。主要器件包括:在硅襯底表面集成激光器(III-V族半導體,以InP為主)、調制器(鈮酸鋰LiNbO3,具有優異的電光效應)、光探測器(Si中摻Ge)、硅波導(Si對于1.31μm/1.55μm通信波段透明)、波分復用及解復用器、耦合器等。

硅光子技術取得了高速發展,技術持續突破。不過,硅光子技術仍面臨以下兩大問題:

1、芯片良率低,成本優勢不明顯:目前,傳統三五族半導體芯片的良率在90%以上,而硅光芯片需要將III-V族半導體鍵合在硅基襯底上。由于硅光集成的工藝尚未成熟,在激光耦合等步驟上的良率較低,導致硅光模塊成本難以進一步提升。

2、硅波導與光纖的耦合效率低,性能優勢不明顯。硅基光波導的尺寸在0.4—0.5μm量級,遠小于單模光纖尺寸(纖芯直徑約8μm—10μm)。尺寸上的差別將導致模場的失配,需要利用硅基波導光柵進行耦合,在耦合過程中將產生損耗。

京公網安備 11010502049343號

京公網安備 11010502049343號