隨著閘極越做越小,制程線寬不斷升級,由10年前的90nm,65nm一直升級到現在的14/16nm,10nm甚至7nm,摩爾定律都在有條不紊著指揮半導體行業前進的路線。但是隨著源極和汲極之間的距離越來越短,半導體工藝的極限逐漸顯露出來。

大多數人都發現了,升級到10nm和7nm所遇到的困難不是捂個被子睡個覺醒來就能解決的,因為除了技術原因還有諸多逐漸浮現出來的不可控因素。

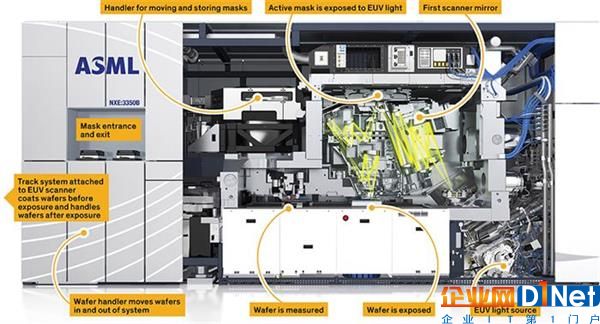

在使用EUV后,線寬的微縮,制程的升級對于缺陷和微粒污染的容忍度將大幅度降低。

制造工具是決定圓晶良品率的關鍵,工具在沉積,蝕刻或清潔過程中有可能受到微粒物污染,這些顆粒物會從上一個生產步驟流入到下一個生產步驟,工藝不一致使得圓晶的特征形狀,覆蓋層和CD(特征尺寸)有偏差,從而導致大范圍缺陷。

給定類型的工藝工具可能彼此不匹配,繼而在通過不同工藝工具生產的圓晶之間產生差異,所有這些問題都會影響產量。

上述的制造過程所造成的差異會成為一個很麻煩的問題,如何理解這個困境?

比如有兩臺打字機,型號價格外觀都一樣,但因裝配環境,零件精度等因素會導致手感有細微差別,因此即使是相同型號的EUV光刻機,有了正確的配置文件,強度恰好的光源,一致的稀有氣體純度,也需要做一些后期工作保證生產結果相同。

換到10、7nm工藝制程的半導體產品上,只要在生產時有個1、2nm的差錯,都有可能造成不可估量的損失。

制程的每一次升級,制造難度都是呈指數級上升,現在我們聽到的工藝名詞最多也只能去到3nm,這是因為到了3nm節點上EUV光刻的隨機性將增大,很難控制好EUV線寬邊緣粗糙度(LER),影響CD和EPE。

同時摩爾定律也會在這個節點附近失效,接下來就是1nm以下的次納米新技術和新材料的天下。

京公網安備 11010502049343號

京公網安備 11010502049343號