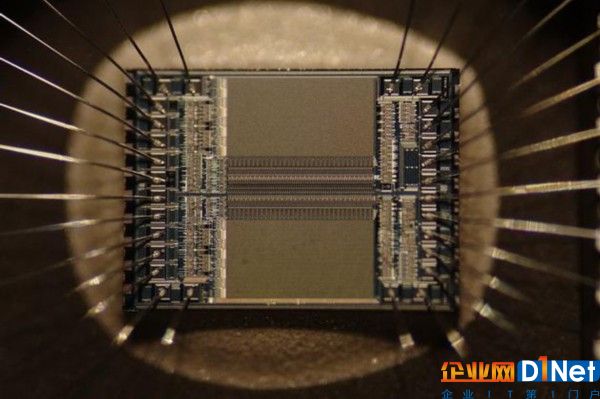

北京時(shí)間3月28日上午消息,美國(guó)麻省理工學(xué)院(MIT)和芝加哥大學(xué)的研究人員開(kāi)發(fā)了一種新技術(shù),可以讓芯片按照預(yù)定的設(shè)計(jì)和結(jié)構(gòu)自行組裝。

這項(xiàng)技術(shù)有望進(jìn)一步推進(jìn)有著50年歷史的“摩爾定律”,從而繼續(xù)壓縮計(jì)算設(shè)備的成本。該研究項(xiàng)目的重點(diǎn)是在芯片上自行組裝線路,而這恰恰是芯片制造行業(yè)最大的挑戰(zhàn)之一。

有了這種技術(shù),就不必像現(xiàn)有的方式那樣在硅片上蝕刻細(xì)微特征,而是可以利用名為嵌段共聚物(block copolymer)的材料進(jìn)行擴(kuò)張,并自行組裝成預(yù)定的設(shè)計(jì)和結(jié)構(gòu)。

MIT化學(xué)工程系教授卡倫·格里森(Karen Gleason)表示,這種自組裝技術(shù)需要向現(xiàn)有的芯片生產(chǎn)技術(shù)中增加一個(gè)步驟。

現(xiàn)在的生產(chǎn)技術(shù)要利用長(zhǎng)波光在硅晶圓上燒制出電路形態(tài)。目前的芯片需要采用10納米工藝,但很難使用同樣的波長(zhǎng)填滿更小的晶體管。EUV光刻技術(shù)有望降低波長(zhǎng),在芯片上蝕刻出更細(xì)微的特征。這種技術(shù)有望實(shí)現(xiàn)7納米工藝,但即便已經(jīng)投資了數(shù)十億美元研發(fā)資金,這種技術(shù)依然很難部署。

MIT認(rèn)為,他們的新技術(shù)很容易融入現(xiàn)有生產(chǎn)技術(shù),無(wú)需增加太多復(fù)雜性。該技術(shù)可以應(yīng)用于7納米生產(chǎn)工藝,有關(guān)這項(xiàng)技術(shù)的論文已于本周發(fā)表在《Nature Nanotechnology》期刊上。

京公網(wǎng)安備 11010502049343號(hào)

京公網(wǎng)安備 11010502049343號(hào)