3D NAND的出現也是因為2D NAND無法滿足人們的需求。NAND閃存不僅有SLC、MLC和TLC幾種類型之分,為了提高其容量、降低成本,NAND的制造工藝也在不斷進步,厚度開始不斷降低,但NAND閃存和處理器還是有很大不同的。雖然先進的工藝帶來了更大的容量,但是其可靠性和性能卻在下降,因為工藝越先進,NAND的氧化層越薄,其可靠性也就越差,廠商就需要采取額外手段彌補這一問題,這必然會提高成本,以至于在達到某個最高點之后完全抵消掉制造工藝帶來的優勢。

3D NAND將思路從提高制造工藝轉移到了堆疊更多層數,這樣就可以兼顧容量、性能和可靠性了。但隨著3D NAND的興起,在價格和競爭壓力期間,3D NAND供應商正準備迎接新的戰斗,相互競爭下一代技術。

NAND美日韓壟斷局面

2016年全球半導體的銷售額之和為3389.31億美元,其中集成電路為2766.98億美元,占82%。但存儲器市場容量約780-800億美元,占全球半導體市場的23%,是僅次于邏輯電路的第二大產品。

從存儲器的種類看,主要分DRAM和Flash,2016年DARM市場容量約414億美元,NAND Flash約346億美元,Nor Flash市場容量較小,約33億美元。據預測2017年,DRAM市場將達到720億美元的規模,DRAM預計將成為2017年半導體行業最大的單一產品類別,超出NAND閃存市場222億美元。

根據OFweek分析師整理的調查報告顯示,目前全世界前十大半導體廠商中,從事內存和閃存芯片的設計與制造的,主要有5家:三星電子、SK 海力士、英特爾、鎂光科技、東芝半導體,韓國和美國的廠商,幾乎已經壟斷了全球的存儲器市場。

DRAM方面,根據某半導體研究中心調查數據顯示2017年第三季度DRAM產業營收數據顯示,三星、SK海力士兩大韓廠的市占各為45.8%與28.7%,合計已囊括74.5%的市占率。美光市占21.0%,三家企業的市占率已達95.5%。

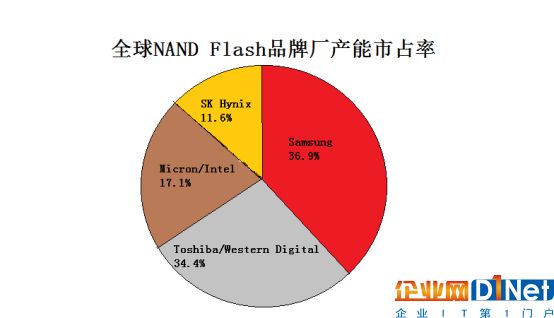

NAND Flash方面,2017年全球NAND Flash品牌廠商產能市占率中,三星占據36.9%、東芝及西數占據34.4%,加上SK海力士、美光及英特爾,五大廠商壟斷市場。

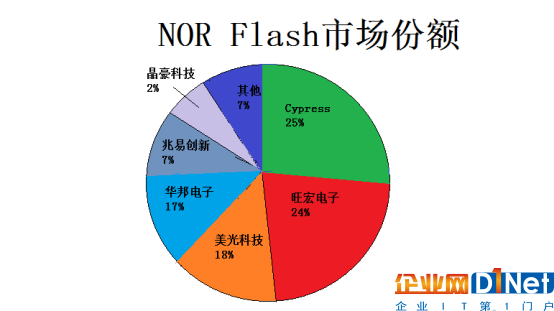

Nor Flash方面,2016年全球市場份額美國Cypress第一25%、臺灣旺宏第二24%、美光第三18%、臺灣華邦第四17%、我國兆易創新第五7%。

以上可見,在占據絕大部分市場容量的DRAM和NAND Flash方面,中國基本為零,僅在市場容量不及DRAM 1/10容量的Nor Flash上有兆易創新入圍。

新玩家進入3D NAND市場,競爭加劇

2018年全球NAND Flash價格一路走跌,由于市場需求增長平緩,業者預期下半年將延續跌勢,隨著國際NAND Flash大廠紛紛加碼投資,2019年QLC NAND將邁入百家爭鳴時代,帶動消費性SSD容量快速升級至TB等級。

另外,據最新消息稱加上長江存儲繼32層3D NAND于2018年底前投入量產,目前Xtacking?架構的64層NAND樣品已經送至合作伙伴進行測試,讀寫質量大致穩定,預計最快將在2019年第3季投產。長江存儲更計劃在2020年跳過96層3D NAND,直接進入128層堆疊,發布新一代3D NAND架構Xtacking。這一系列舉動都標志著長江存儲試圖超車追趕國際大廠,因此,全球NAND Flash產量持續增加,戰火愈益激烈,2019年NAND Flash市場恐將大幅震蕩。

長江存儲采用Xtacking?架構的64層3D NAND跟傳統架構的96層相比,容量僅低15%左右,據OFweek小編整理的數據,預計2020年其推出的128層堆疊可與國際大廠展開競爭,同時也標志著我國的閃存技術又邁向了新的高峰。

擴展3D NAND

3D NAND是當今平面NAND閃存的后續產品,用于存儲應用,如智能手機和SSD。與平面NAND不同,3D NAND類似于垂直摩天大樓,其中水平層的存儲器單元被堆疊,然后使用微小的垂直通道連接。

3D NAND通過設備中堆疊的層數來量化,隨著更多層的添加,位密度增加。在研發方面,供應商也在開發下一代技術,分別為256層和512層。

其實這就是一場比賽,是最高籌碼間的競賽。現有的3D NAND供應商:英特爾、美光、三星、SK海力士和東芝,他們都并沒有停滯不前,并在競爭中保持領先地位,但是每個供應商都采用兩種方法:單層、串堆疊來擴展3D NAND。

傳統架構的96層,雙層堆疊已經略顯常規,其中會加入一些單層堆疊。在單層方法中,供應商一次性制造單個設備。理論上,這可以降低成本和周期時間。但在晶圓廠,單層方法很難實現。

3D NAND挑戰從光刻轉向沉積和蝕刻

在晶圓廠中,3D NAND與平面NAND不同。在2D NAND中,該過程取決于使用光刻縮小尺寸,雖然光刻仍然用于3DNAND,但它不是最關鍵的一步。對于3D NAND,挑戰從光刻轉向沉積和蝕刻。

3D NAND流以襯底開始。然后,供應商在流動交替堆疊沉積中經歷了第一個挑戰。使用CVD,該方法包括在襯底上沉積和堆疊交替的薄膜。

首先,在基板上沉積一層材料,然后在頂部上施加另一層。該過程重復幾次,直到給定的設備具有所需的層數。

每個供應商使用不同的材料例如,三星在基板上沉積交替的氮化硅和二氧化硅層,這取決于你制造的器件類型,可以在基板上堆疊數百層。但隨著更多層的添加,面臨的挑戰是在高產量下堆疊具有精確厚度和良好均勻性的層。壓力和缺陷控制面臨巨大挑戰。此外,堆疊往往在壓力下彎曲,尤其在單層方法中表現明顯。為此,供應商將在基板上堆疊96層薄膜。

避免壓力的另一種方法是使用串型堆疊。例如,將圖層存放在一個48層設備上,然后在另一個設備上重復該過程,形成一個96層產品。通常,48層交替堆疊沉積工藝是成熟的并且產生相對較小的應力,但是存在挑戰。之后,在膜疊層上施加硬掩模,并在頂部圖案化孔。然后,這是流動高縱橫比(HAR)蝕刻中最難的部分。

為此,蝕刻工具必須從器件疊層的頂部到底部基板上鉆出微小的圓孔或通道。通道使得單元在垂直堆疊中彼此連接。一個器件可能在同一芯片中有250萬個微小通道。每個通道必須平行且均勻。簡單來說,蝕刻器通過用離子轟擊表面來產生微小的通道,但這種蝕刻非常困難且非常耗時,根據蝕刻中縱橫比縮放的基本定律表明,縱橫比越高,沉積層的厚度越大,孔越小,蝕刻越慢。隨著蝕刻工藝更深地滲透到通道中,離子的數量可能減少。這會降低蝕刻速率。更糟糕的是,可能會發生不需要的CD變化。

因此,可以想象供應商可以使用串型堆疊從96層遷移到128層以上。理論上,使用傳統的蝕刻工具,供應商可以處理兩個64層設備,從而實現128層。傳統的蝕刻器涉及在室溫下交替蝕刻和鈍化步驟的過程。相反,低溫蝕刻在低溫下進行,大大提高了蝕刻速率,雖然低溫蝕刻是困難且昂貴的,但其好處超過了增加的成本。

京公網安備 11010502049343號

京公網安備 11010502049343號