云計(jì)算已經(jīng)成為數(shù)據(jù)中心市場(chǎng)中增長(zhǎng)最快的部分。事實(shí)上,根據(jù)思科全球云指數(shù)預(yù)測(cè),未來(lái)幾年內(nèi),云計(jì)算將增長(zhǎng)三倍,到2021年,云計(jì)算將占到所有數(shù)據(jù)中心流量的95%。這種增長(zhǎng)的一個(gè)關(guān)鍵部分是虛擬化,它允許動(dòng)態(tài)分配計(jì)算實(shí)例和工作負(fù)載,以跟上云服務(wù)的動(dòng)態(tài)特性。

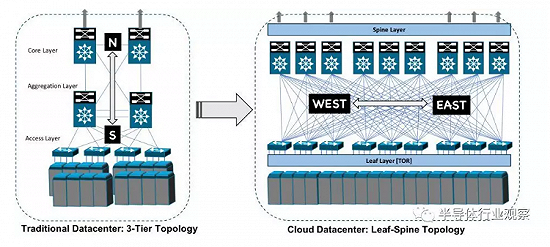

從另一個(gè)角度來(lái)看,現(xiàn)在超過(guò)75%的流量在數(shù)據(jù)中心中東西向逐個(gè)服務(wù)器地流動(dòng)。這引發(fā)了第一組問(wèn)題,因?yàn)閭鹘y(tǒng)的三層網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)是針對(duì)南北客戶端—服務(wù)器流量進(jìn)行優(yōu)化的,因此無(wú)法有效處理這類數(shù)據(jù)流。

為了解決數(shù)據(jù)流轉(zhuǎn)移問(wèn)題,并最大限度地減少延遲和瓶頸,云數(shù)據(jù)中心正在轉(zhuǎn)向葉脊(leaf-spine)拓?fù)洌渲忻總€(gè)葉服務(wù)器可以通過(guò)脊進(jìn)行單跳(single hop),訪問(wèn)其他葉服務(wù)器。

Cadence Design Systems接口IP高級(jí)產(chǎn)品營(yíng)銷經(jīng)理Muthukumar Vairavan表示:“在葉脊拓?fù)浣Y(jié)構(gòu)中,每片葉都要連接到每個(gè)脊開(kāi)關(guān)。因此,可以支持的主機(jī)數(shù)量以及網(wǎng)絡(luò)帶寬擴(kuò)展現(xiàn)在變成了交換機(jī)設(shè)備端口數(shù)量和每個(gè)端口帶寬的函數(shù)。交換機(jī)的帶寬主要取決于交換機(jī)ASIC和可安裝在單個(gè)機(jī)架單元中的光學(xué)模組數(shù)量。”

目前,最先進(jìn)的交換機(jī)ASIC擁有多達(dá)256條PAM-4 SerDes信道,每條信道的運(yùn)行速度為56Gbps,總帶寬為12.8Tbps。Vairavan表示:“總的來(lái)說(shuō),這種交換機(jī)最多可以支持32個(gè)端口400GbE(8條線路,每條56Gbps)。但是,隨著超大規(guī)模數(shù)據(jù)中心對(duì)帶寬的需求不斷增加,交換機(jī)廠商希望將芯片帶寬提高一倍,達(dá)到25.6Tbps。傳統(tǒng)上,這是通過(guò)將SerDes信道速度加倍來(lái)實(shí)現(xiàn)的,而光學(xué)網(wǎng)際互聯(lián)論壇(OIF)正致力于定義112Gbps SerDes規(guī)范,以實(shí)現(xiàn)這一目標(biāo)。”

在這樣的速度下所面臨的挑戰(zhàn)是,信道損耗非常高,而且SerDes需要很多均衡。采用先進(jìn)的DSP技術(shù)對(duì)信號(hào)進(jìn)行恢復(fù),這可能導(dǎo)致顯著的功耗。Vairavan建議,為了解決這個(gè)問(wèn)題,平臺(tái)設(shè)計(jì)需要轉(zhuǎn)向更好的PCB材料,使用有源電纜和重定時(shí)器,以保持在這樣的速度下信道損耗可控。“另一項(xiàng)新興技術(shù)是板載光學(xué)(OBO),光學(xué)芯片靠近電路板上的交換機(jī)ASIC放置,因此減少了電子信道。 通過(guò)將光學(xué)元件從面板移走,OBO還可以提供更好的密度和冷卻效果。OIF指定了許多類別的SerDes規(guī)范,如Long-Reach,Medium-Reach,Short-Reach等,以便對(duì)特定的交換機(jī)配置進(jìn)行正確的SerDes性能/功率權(quán)衡。”

雖然構(gòu)建其中一個(gè)芯片需要許多IP,但有四個(gè)項(xiàng)目通常會(huì)引發(fā)討論——SerDes、HBM PHY、網(wǎng)絡(luò)級(jí)片上存儲(chǔ)器,以及TCAM(內(nèi)容可尋址存儲(chǔ)器)。

eSilicon公司營(yíng)銷副總裁Mike Gianfagna表示:“SerDes需要實(shí)現(xiàn)高速片外通信。HBM PHY需要將2.5D封裝的HBM堆棧內(nèi)存連接到ASIC上。網(wǎng)絡(luò)級(jí)片上存儲(chǔ)器就像雙端口和偽雙端口存儲(chǔ)器一樣,針對(duì)極高速度進(jìn)行了優(yōu)化,TCAM用于實(shí)現(xiàn)高效的網(wǎng)絡(luò)數(shù)據(jù)包路由。”

Gianfagna指出,IP問(wèn)題還有另外兩個(gè)方面。“首先,經(jīng)過(guò)芯片驗(yàn)證的高質(zhì)量IP非常重要,但還不夠。還必須驗(yàn)證IP可以協(xié)同工作。諸如可測(cè)試性策略、操作點(diǎn)和金屬疊層之類的東西——這種兼容性大大降低了整合風(fēng)險(xiǎn)。其次,IP必須在考慮最終應(yīng)用的情況下進(jìn)行配置。 其中包括編譯內(nèi)存和TCAM等內(nèi)容,以支持SerDes的不同配置要求和可編程性能。”

位置,位置,位置

然而,沒(méi)有一種方法可以適用于所有情況。一個(gè)系統(tǒng)公司想要從它的IP供應(yīng)商那里得到什么芯片取決于芯片的設(shè)計(jì)應(yīng)用。

Synopsys公司高速SerDes產(chǎn)品營(yíng)銷經(jīng)理Manmeet Walia表示:“有多種方法看待這個(gè)問(wèn)題。首先,你要在更廣泛的層面上認(rèn)清楚你所服務(wù)的市場(chǎng)是什么,無(wú)論是企業(yè)、校園、數(shù)據(jù)中心(現(xiàn)在被稱為超大規(guī)模數(shù)據(jù)中心),還是電信基礎(chǔ)設(shè)施。如果把它們按規(guī)模排列,那么企業(yè)要排在第一位,它們是較小的數(shù)據(jù)中心。然后是云提供商——谷歌、facebook、亞馬遜——這就是所謂的超大規(guī)模數(shù)據(jù)中心。最后是服務(wù)提供商,如ATT等。根據(jù)你所服務(wù)的對(duì)象,三種規(guī)模的需求各不相同。”

第二個(gè)因素涉及到這些公司所需要的具體功能。Walia表示:“無(wú)論是CPU芯片組、GPU、加速器、適配器卡、交換機(jī)、存儲(chǔ)陣列還是安全系統(tǒng),根據(jù)它們的功能,又會(huì)出現(xiàn)不同的要求。第三,從PHY的角度來(lái)看,它們?cè)谙到y(tǒng)中的位置很重要,無(wú)論是在刀片服務(wù)器卡內(nèi),還是在中間卡上,或是在交換機(jī)架的頂部。所以它們的位置決定了它們的需求。市場(chǎng)整體上非常分散,因?yàn)樗兊迷絹?lái)越復(fù)雜。”

Walia說(shuō),除此之外,還有一群開(kāi)發(fā)人員在談?wù)撔酒驗(yàn)樗鼈儽槐频搅诵酒闫叽缁蚬庹值倪吘墶?ldquo;他們現(xiàn)在想要進(jìn)入chiplets,我們正在從那些想要做所謂的USR(超短距離)SerDes的客戶那里獲得需求。這是另一個(gè)需要解決的市場(chǎng)。”

今天,大多數(shù)網(wǎng)絡(luò)設(shè)計(jì)活動(dòng)都在云端,其中大部分都是由AI和機(jī)器學(xué)習(xí)應(yīng)用驅(qū)動(dòng)的。Walia表示:“有趣的是,所有網(wǎng)絡(luò)公司現(xiàn)在都在嘗試遵循垂直整合模式,他們甚至在嘗試自己制作芯片組。無(wú)論是中國(guó)的阿里巴巴、騰訊、百度,還是美國(guó)的Facebook、谷歌,都在嘗試自己的AI芯片組。他們不想使用商業(yè)芯片。因此,至少?gòu)腎P的角度來(lái)看,我們的業(yè)務(wù)指標(biāo)不是芯片量。更多的是從設(shè)計(jì)開(kāi)始的,當(dāng)然,我們?cè)诖颂幙吹搅嗽朴?jì)算驅(qū)動(dòng)了我們大部分IP業(yè)務(wù)。”

西門子Mentor事業(yè)部IP部門總經(jīng)理Farzad Zarrinfar對(duì)此表示贊同:“基本的處理器并沒(méi)有達(dá)到要求,所以我們看到主要的OEM、搜索領(lǐng)導(dǎo)者、游戲領(lǐng)導(dǎo)者和通信領(lǐng)導(dǎo)者都在開(kāi)發(fā)他們自己的ASIC。顯然,這些ASIC很多取決于應(yīng)用。如果它是數(shù)據(jù)中心應(yīng)用,或是某種汽車應(yīng)用,亦或物聯(lián)網(wǎng)應(yīng)用,我們就會(huì)看到很多構(gòu)建模塊。例如,如果你觀察一個(gè)三層千兆交換機(jī),那么你就會(huì)發(fā)現(xiàn)1千兆位和10千兆位MAC(媒體訪問(wèn)控制器)。有些人在芯片內(nèi)部加入了ASIC、收發(fā)器、SerDes和PHY,以進(jìn)一步提高整合度,并最大限度地降低成本。有些人希望基于自己的架構(gòu)來(lái)保持它。他們使PHY和SerDes具有更大的幾何形狀,并且在芯片外使用它們,他們將更大的幾何結(jié)構(gòu)用于SerDes。然后,在純數(shù)字部分,他們將工藝推進(jìn)到10nm和7nm,甚至可以降至5nm finFET技術(shù)。”

Walia說(shuō),這種模式在過(guò)去幾年中迅速出現(xiàn)。最初,這些公司開(kāi)發(fā)低端應(yīng)用,比如攝像頭,但現(xiàn)在他們正在轉(zhuǎn)向高端數(shù)據(jù)中心,并完成越來(lái)越多的工作。

對(duì)于AI / ML應(yīng)用而言,芯片主要是許多帶有ARM 64位處理器的SerDes。Walia表示:“這是一組ARM高端處理器,周圍是SerDes。它們通過(guò)SerDes使這些核心能夠以非常快的速度互相通信,然后這些SerDes也以盒子對(duì)盒子的方式與其他類似的設(shè)備通信。從本質(zhì)上講,它是一個(gè)輸入和一個(gè)輸出,但它們之間發(fā)生的是一個(gè)指令集,允許它們?cè)谝欢螘r(shí)間內(nèi)通過(guò)可重復(fù)性,以及讀取人類行為或其他數(shù)據(jù)來(lái)接受訓(xùn)練,所以它允許自我編程,允許在一段時(shí)間內(nèi)學(xué)習(xí),這就是它們需要強(qiáng)大處理能力的原因。”

網(wǎng)絡(luò)設(shè)計(jì)的另一個(gè)方面涉及密度要求。Walia表示:“如今,這些都轉(zhuǎn)化為整合的挑戰(zhàn)。整合變得越來(lái)越重要,我們一直在與想要整合多達(dá)300條SerDes信道(某些情況下甚至達(dá)到500條)的客戶進(jìn)行交流,這要求我們作為IP供應(yīng)商為他們提供很多服務(wù),以便他們可以整合這些SerDes。這個(gè)區(qū)域需要非常小,即前端需要非常窄,以便沿著PHY的邊緣放置越來(lái)越多的SerDes。另外,我們現(xiàn)在需要在兩個(gè)方向上都有PHY,以便設(shè)計(jì)團(tuán)隊(duì)能夠最舒服地將它們放入芯片的所有四個(gè)側(cè)面。這是因?yàn)樵?8nm以下,臺(tái)積電不允許我們翻轉(zhuǎn)多邊形方向。但這意味著我們必須有兩個(gè)不同的設(shè)計(jì)和兩個(gè)不同的布局,以便他們可以有效地將這些SerDes放在四個(gè)側(cè)面。除此之外,我們還必須允許它們?cè)趦?nèi)部有多個(gè)層次——基本上要在IP內(nèi)部包含兩級(jí)、三級(jí)深度的SerDes。”

與此同時(shí),Walia指出,OEM正在越來(lái)越多地采用封裝凸點(diǎn)技術(shù)(packaging bump technology),而不是采用標(biāo)準(zhǔn)的C4凸點(diǎn)(C4 bumps)。“很可能他們正在使用插入式方法(interposer-type),所以他們需要更寬,并且凸點(diǎn)可能需要有犧牲pad或微凸點(diǎn)技術(shù)(microbump technology)。從本質(zhì)上講,需要大量的凸點(diǎn)定制以及許多后端服務(wù)。你如何把所有這些東西放在一起?如何把所有這些信號(hào)帶到封裝基板上?如何把它們放入SoC?如何以1GB /秒或類似的速度進(jìn)行時(shí)序收斂?所有這些都是巨大的挑戰(zhàn),所以當(dāng)我們提供這些IP時(shí),我們必須提供很多關(guān)于如何使用它們的指導(dǎo)。過(guò)去我們認(rèn)為,IP非常難以設(shè)計(jì),但易于整合。但現(xiàn)在不是這樣了。它們不但很難設(shè)計(jì),而且更加難以整合。”

管理IP

如今設(shè)計(jì)的許多高級(jí)網(wǎng)絡(luò)芯片組和ASIC都以數(shù)據(jù)中心為目標(biāo),其中功耗、性能和面積都是關(guān)鍵因素。它也是芯片制造商最賺錢的領(lǐng)域之一。

ClioSoft公司營(yíng)銷副總裁Ranjit Adhikary表示:“這就是云計(jì)算領(lǐng)域正在發(fā)生的一切。每個(gè)人都想把東西放在云端,云端市場(chǎng)正在增長(zhǎng)。鑒于此,每個(gè)數(shù)據(jù)中心公司都希望降低成本,因此功耗和可靠性成為非常重要的組成部分。當(dāng)你討論下一代網(wǎng)絡(luò)交換機(jī)、定義一個(gè)平臺(tái)時(shí),你需要確保I/O帶寬和內(nèi)存子系統(tǒng)都能夠提供所需的性能。因此,你基本要確保所有IP都可以即插即用。你需要確保它們都有相同的金屬疊層、可靠性要求、工作范圍、控制接口——甚至相同的DFT方法。當(dāng)你現(xiàn)在談?wù)撨@些事情的時(shí)候,IP管理平臺(tái)就變成了一個(gè)重要組成部分,因?yàn)榈筋^來(lái)你總是希望可以獲得你想要的IP。你想知道參數(shù)是什么,于是下載它,查看它,從而無(wú)需經(jīng)過(guò)一個(gè)漫長(zhǎng)的周期來(lái)確定IP是否有效,或者到處尋找支持?jǐn)?shù)據(jù)在哪里。”

找到各種IP區(qū)塊并確定它們是否在其他地方被使用至關(guān)重要。Adhikary表示:“許多公司將為不同的代工廠提供不同的PDK,設(shè)計(jì)團(tuán)隊(duì)需要知道IP是否經(jīng)過(guò)代工廠驗(yàn)證,或者同一公司的其他客戶是否正在使用它。你想知道IP的可靠性。例如,它投入生產(chǎn)了嗎?有什么問(wèn)題嗎?最終,問(wèn)題歸結(jié)為文檔記錄的功耗、性能和面積有多好。我們?cè)诖蠖鄶?shù)公司中發(fā)現(xiàn),信息并不全都集中在一個(gè)地方,因此把IP管理系統(tǒng)與文檔控制系統(tǒng)聯(lián)系起來(lái)變得很重要,這樣每個(gè)人都能保持同步,而這僅僅是個(gè)開(kāi)始。”

展望未來(lái)

隨著云服務(wù)提供商把25.6Tbps交換機(jī)遷移到51.2Tbps,傳統(tǒng)的擴(kuò)展技術(shù)似乎不太可能滿足需求。

Walia表示:“交換機(jī)ASIC是在先進(jìn)技術(shù)節(jié)點(diǎn)上實(shí)現(xiàn)的,以利用增加的密度和更低的功率,但正在觸到光罩和產(chǎn)量的極限。一種迅速普及的選擇是芯片分解,大型芯片被分解為可管理的芯片尺寸,然后使用高速、低功耗的封裝內(nèi)互連技術(shù)整合到多芯片模組(MCM)封裝內(nèi)。另一種選擇是將邏輯芯片和SerDes分開(kāi),并將它們放在MCM中。通過(guò)轉(zhuǎn)向封裝內(nèi)光學(xué),可以獲得51.2Tbps所需的更大的光學(xué)密度,所謂封裝內(nèi)光學(xué)是將光學(xué)芯片與MCM中的開(kāi)關(guān)ASIC芯片整合到一起,以實(shí)現(xiàn)異構(gòu)系統(tǒng)級(jí)封裝(SiP)。然后可以將光纖連到面板或尾纖上。”

交換機(jī)ASIC和高速光電互連是云時(shí)代數(shù)據(jù)中心的支柱。為了滿足這些數(shù)據(jù)中心帶寬的爆炸性增長(zhǎng),交換機(jī)ASIC制造商、光學(xué)和互連IP供應(yīng)商和標(biāo)準(zhǔn)機(jī)構(gòu)需要建立生態(tài)系統(tǒng)。未來(lái)的解決方案將圍繞異構(gòu)解決方案展開(kāi),這些解決方案將為特定的應(yīng)用和獨(dú)特的數(shù)據(jù)流量身定制,以滿足新的性能、功耗和可擴(kuò)展需求。

京公網(wǎng)安備 11010502049343號(hào)

京公網(wǎng)安備 11010502049343號(hào)