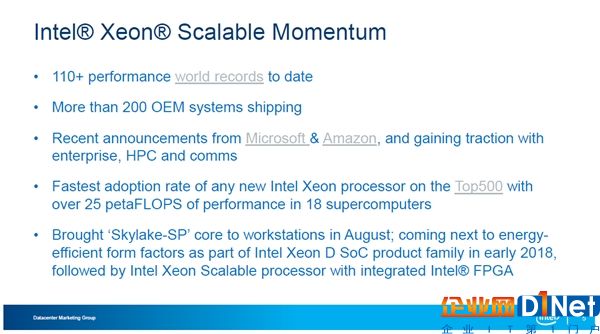

Intel日前對外發布了詳細的Benchmark跑分報告,主旨是凸顯自家Xeon Scalable處理器比AMD EPYC是何等優秀。

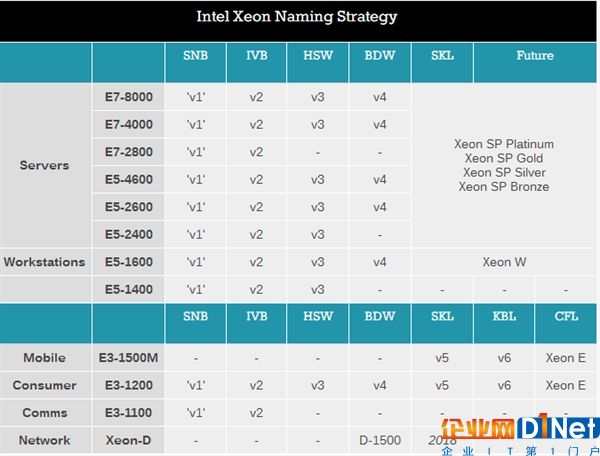

PPT中,Intel還透露了Xeon D的情況,預計2018年早些時候推出,內建Skylake-SP處理器架構,FPGA的形式對外出貨。

Xeon-D第一代于2015年11月推出,CPU基于 Broadwell,最高8核,萬兆以太網支持,熱設計功耗45W,產品主要用在并行數量要求較高(去年2月升級到16核)的微機、網絡存儲設備、防火墻等領域,所以ARM在這一領域也頗有作為。

Skylake-SP是目前Intel設計最先進的處理器架構,支持AVX-512指令集。

因為AVX-512單元要占到處理器面積的20%以上,所以即便Intel從14nm Broadwell升級為14nm+的Skylake,Anandtech預計這顆SoC的面積仍然會增加。

京公網安備 11010502049343號

京公網安備 11010502049343號