西部數據(WD)于今日宣布其已開始生產業內最密集的 3D NAND 閃存芯片,堆疊達到了 64 層。當然,每單元存數比特位數也從 2 增加到了 3(說白了就是從 MLC 變成了 TLC)。西數及其合作伙伴東芝將其“垂直 3D 堆疊技術”稱作 Bit Cost Scaling(簡稱 BiCS),而西數方面也已開產首批 64 層 @ 512 Gb 的 3D NAND 芯片。

上圖來自東芝

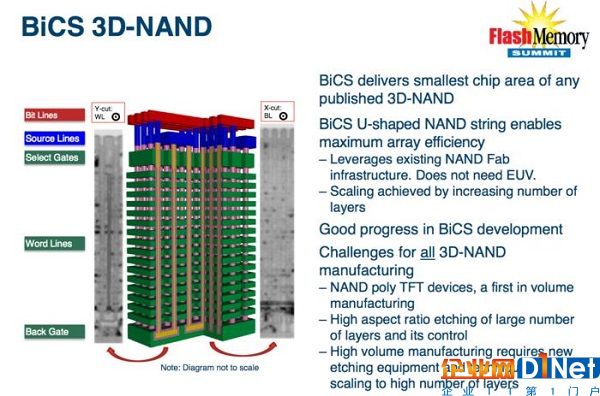

其生產過程與摩天大樓的建造類似,能夠在較小的地面上組合出密集的結構,使得每 Gb 的成本效益更加明顯。此外,這項技術還增加了數據可靠性、以及固態存儲是速度。

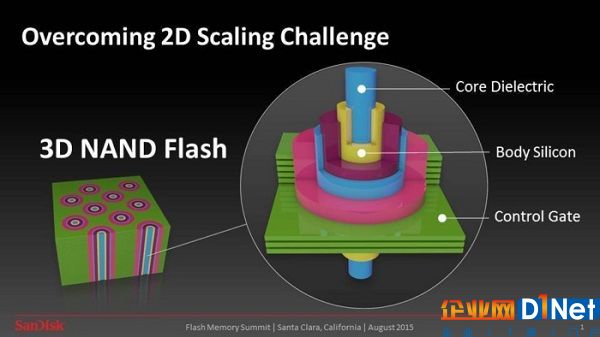

3D NAND 讓制造商們可以克服 NAND 閃存的物理限制,因為隨著晶體管尺寸接近 10nm,其進一步收縮的能力將迅速消散。

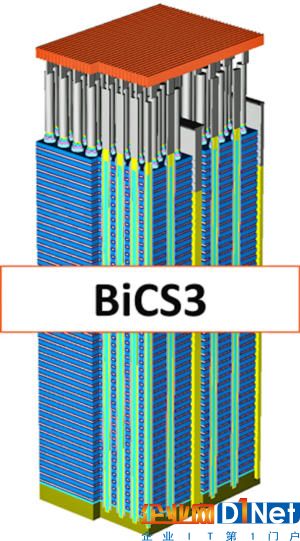

西數 BiCS 3D NAND 閃存結構圖(64 層堆疊)

最新 3D NAND 閃存已經用到了一片外形如同口香糖般大小、但容量高達 3.3 TB 的固態硬盤(SSD)驅動器上。如果采用 2.5 英寸的外形,其容量更可輕松超過 10 TB 。

除了三星和東芝,英特爾和鎂光也在生產 3D NAND 產品。

三星是首家宣布量產 3D 閃存芯片的企業(2014 年),其技術被命名為 V-NAND,起初只堆疊了 32 層,但也將存儲位元從 MLC 改進到了 TLC。所以其 TLC 產品的容量(128 Gbits / 16 GB)比東芝初代 48 層 NAND 芯片還要高)。

西數于 2016 年 7 月首次向公眾展示了其 64 層 3D NAND 技術,新芯片已于日本四日市制造工廠開始試產,該公司計劃在 2017 年 下半年開始量產。

京公網安備 11010502049343號

京公網安備 11010502049343號