在第18屆中國國際工業博覽會上,上海兆芯公司的ZX-C處理器獲得了金獎。在2017年3月,更是接連榮獲“2017年度大中華IC設計成就獎”(見圖22)、“第十一屆(2016年度)中國半導體創新產品和技術獎”。在國家十二五科技創新成就展中兆芯的宣傳材料顯示,“兆芯國產X86通用處理器的成功自主研發和量產,令國產處理器在性能方面完成了一次跨越式的提升,從十二五初期的不足國際整體水準的10%提升到了目前的80%”。

眾所周知,Intel對X86的授權有著極為嚴格的限制,那么上海兆芯的X86芯片技術到底從何而來?ZX-C目前的短板在哪里?在性能上和Intel相差多遠呢?

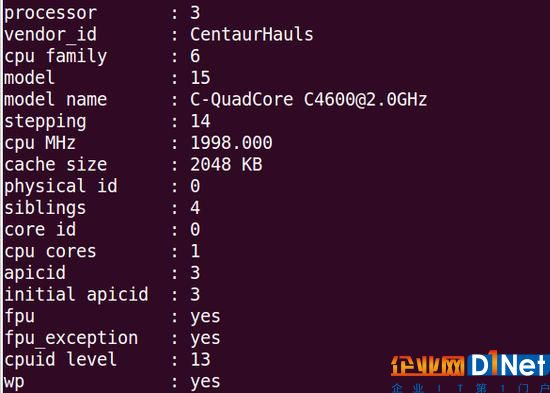

兆芯C4600 cpuinfo的信息顯示:設計廠商為美國Centaur,微結構是VIA的以賽亞

在Linux系統中命令cat /proc/cpuinfo可以讀出芯片的一些信息和特性。其命令和Windows系統中cpu-z軟件獲得的信息類似。芯片cpuinfo的信息是通過CPUID指令讀出來的。例如eax=1時,讀出的是處理器的信息以及特征位(CPUID指令的使用,見en.wikipedia.org/wiki/CPUID)。

從圖1兆芯C4600芯片cpuinfo的信息可以看出,這個芯片的廠商(vendor_id)為CentaurHauls,即Centaur公司。其中cpu family表示那一代芯片,其中的family 6表示VIA的Nano系列。其中的model表示型號,也就是采用哪種微結構,15表示以賽亞。model name為處理器的型號,圖中為C-QuadCore [email protected]。表示4核芯片C4600,主頻為2GHz。

圖1兆芯C4600芯片cpuinfo的信息

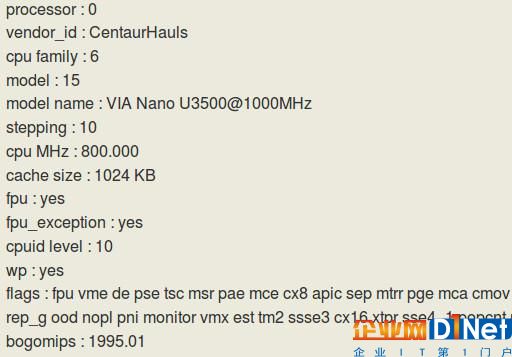

圖2威盛Nano U3500芯片cpuinfo的信息

圖2給出了威盛公司的Nano U3500芯片cpuinfo的信息,其model name為VIA Nano U3500@1000MHz。對比vendor_id的信息可以看出都是VIA的Centaur公司,對比cpu family和model的信息,也可以看出都是family 6和model 15,即都是 “以賽亞”架構。

圖3 威盛Nano U3500芯片的信息

從圖3可以看出U3500芯片屬于VIA Nano系列。其中的微架構為Isaiah(以賽亞)。支持的指令集到SSE4.1為止,并且支持x86-64指令集。

從C4600芯片cpuinfo的信息可以看出,C4600的設計廠商(vendor_id)還是VIA的Centaur公司,而沒有改為ZX的標志。

美國Centaur公司和Glenn Henry

根據維基的資料顯示:Centaur(半馬人)科技公司,創立于1995年,創建者為Glenn Henry, Terry Parks, Darius Gaskins和Al Sato,其獲得的投資來自于IDT公司。其公司的目標是開發兼容的x86處理器,目標定位為開發比Intel公司的x86芯片價格更低,功耗更小的芯片。早期的產品稱為WinChip,1999年9月,Centaur被IDT公司出售給VIA公司,其后續的產品為VIA C3和VIA C7,以及VIA Nano。Centaur公司的芯片主要面向嵌入式市場,包括移動市場,也就是面積更小、價格更便宜,功耗更低的x86芯片市場。Centaur的設計理念是對于面向特定市場需求“夠用就好”。VIA Nano Isaiah(以賽亞),是Centaur第一款超標量、亂序執行的CPU,第一款64位的CPU,Nano芯片這時更為強調性能,而不再是追隨性能功耗比的等式,但是其維持和C7相同的功耗(TDP)。

根據Centaur(半馬人)公司的網站的介紹,Centaur(半馬人)科技公司,位于德克薩斯-奧斯丁。主要設計高性能、低功耗的x86兼容的微處理器,號稱具有最快的設計流程,設計周期是競爭對手廠商的三分之一。該公司沒有管理者,所有的工程師直接向Centaur公司的創建者和總裁Glenn Henry匯報,Glenn Henry是前DELL公司的CTO和IBM的工程系列的Fellow(20年的Fellow)。1999年8月,Centaur公司被VIA公司收購。但是這次收購沒有改變Centaur的文化,也就是Centaur作為VIA公司的子公司獨立地運營,而不會受到VIA的影響。在Cyrix解散后,VIA公司的x86芯片的設計都是來自于Centaur公司,而VIA QuadCore C4650芯片也是出自Centaur公司的Glenn Henry之手。

圖4 Glenn Henry

這里介紹以下Glenn Henry。Glenn Henry于1967年加入IBM,在IBM干了21年,擔任首席架構師,是RISC工作站、AIX操作系統和AS/400等創新產品的主要研發管理者,于1985年獲得IBM fellow的稱號,1988年離開IBM加入DELL公司,為DELL公司負責研發的副總和CTO,1994年離開DELL公司,擔任MIPS公司的咨詢顧問,試圖把x86和MIPS架構結合在一起,1995年Henry獲得了來自IDT公司的投資,創建了Centaur公司,設計低功耗、低成本的x86處理器。

揭開以賽亞神秘的面紗

正如Intel在研發出酷睿2后一舉翻身,AMD在開發出Zen之后終于做出能與Intel相比較的產品,一款CPU最關鍵的就在于其微結構,那么QuadCore C4650芯片的微結構究竟怎么樣呢?

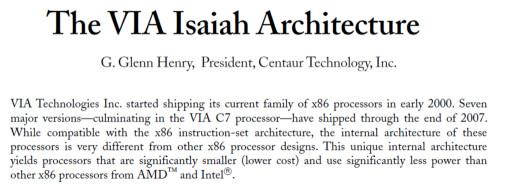

圖5 The VIA Isaiah Architecture

Centaur公司的靈魂人物和總裁和Glenn Henry撰寫的一篇文章“The VIA Isaiah Architecture”(圖5),文章中分析了為什么采用3發射、亂序執行結構,和Intel的Core比較起來有什么優勢,為了降低功耗,采用了什么樣的權衡。文章介紹的非常詳細,有興趣的網友可以找原文品讀。

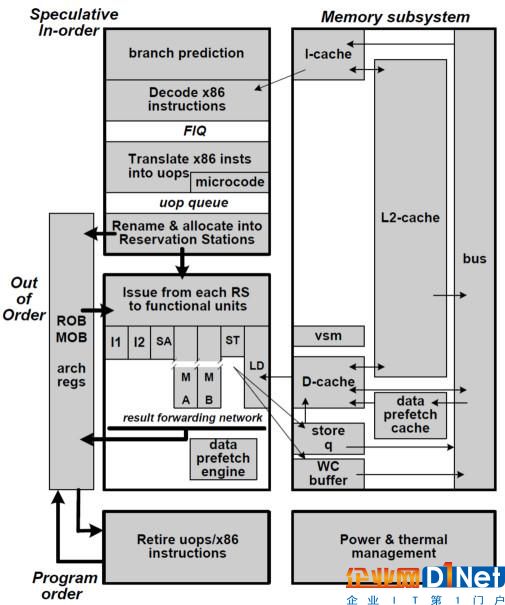

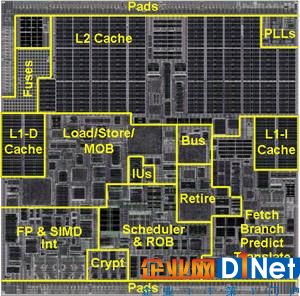

從圖6中可以看出,以賽亞采用類似于Core架構的設計,7個部件,2個定點I1和I2,2個浮點MA和MB,1個取數LD,1個存數ST和1個SA地址計算。也就是2個定點、2個浮點、2個訪存。屬于中規中矩的設計。

圖6 以賽亞微結構框圖

Cache的設計為64KB+64KB L1 cache,16路組相聯,2MB的uninclusive的L2 cache。保留站的項數為76項(micro-ops,其micro-ops類似Intel處理器的uops,每條X86指令對應1-3條uops),規模和Intel的Core以及AMD的K10基本相當。其也采用了大量的低功耗技術,例如為了降低功耗,分支預測器的表項只有4K項,取指令時只取16字節大小等。

從文章中介紹和測試數據來看,該處理器結構在2008年而言是非常棒的微架構,兼顧了低功耗和適度性能。從性能上可以打贏當時的按序發射的Intel Atom,但是由于技術團隊人數有限,在功耗控制實現上不是那么完美,所以導致其市場定位高不成低不就。在高性能上沒法和Intel的Core和AMD的K10抗衡,在低功耗上又不能做到無風扇設計,沒法和Atom以及近年來崛起的ARM相比。導致Nano的芯片主要用于上網本等市場,但是由于出貨量較少,每片的成本相對較高,隨著上網本市場的消亡,Nano芯片基本也退出了主流市場。

Glenn Henry曾在2008年接受記者Dave Altavilla的采訪,在采訪中Glenn Henry對低功耗的以賽亞架構處理器的一些解釋(“VIA's Glenn Henry Speaks On New Low Power Isaiah Processor,by Dave Altavilla, January, 2008”)。以下為采訪鏈接:

圖7 Glenn Henry介紹“以賽亞”架構

圖8 “以賽亞”架構Nano處理器版圖

ZX-C QuadCore C4600和VIA QuadCore C4650關系密切

根據媒體報道:

《真正走向市場化,揭秘中國兆芯X86處理器》

《國貨新貴 兆芯X86處理器來了!--開先ZX-C C4600處理器體驗》

《兆芯傅城:國產X86通用處理器已接近國際水平》

這三篇報道算是比較全面的介紹兆芯的X86處理器。文章中介紹了是兆芯公司打造了中國X86 CPU,也介紹了兆芯ZX-C四核心處理器,ZX-C處理器是國家“十二五”核高基重大科技專項創新成果,采用28nm工藝等內容。

不過,這些報道中的一些內容經不起對敲,比如文章中稱:兆芯ZX-C四核處理器的推出,讓國產處理器的性能完成了從“十二五”初期不足國際主流水準10%到目前80%的跨越性提升。

其實,這段話并非媒體妄言,而是出自兆芯(VIA Alliance Semiconductor)在“十二五”科技成果展上的宣傳資料。不過,兆芯官方宣傳資料中達到國際主流水準的80%是不客觀的。

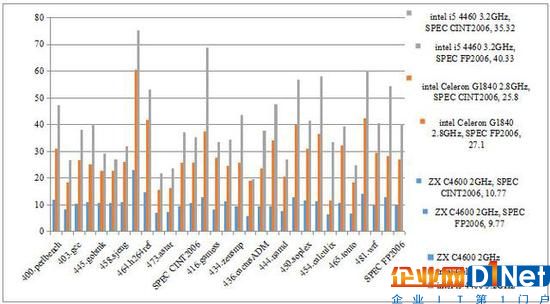

但經過實際測試,即便是兆芯ZX-C四核處理器中主頻達到2.0G的C4600,與Intel G1840和I5 4460相比較。從圖10可以看出,就定點而言,I5 4460是ZX-C的3.3倍,G1840是ZX-C的2.4倍。就浮點而言,I5 4460是ZX-C的4.4倍,G1840是ZX-C的2.8倍。在這種情況下,宣稱ZX-C達到國際主流80%,存在虛假宣傳行為。

(圖10)

言歸正傳,一起先來探究以下ZX-C處理器和VIA QuadCore C4650的關系。

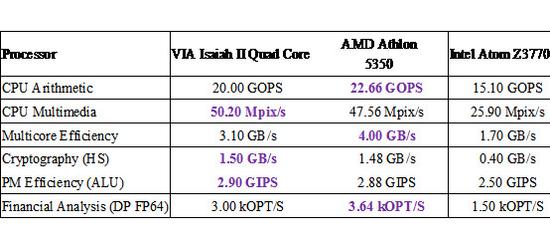

根據2014年的報道“Report: VIA’s quad-core, 64-bit Isaiah II chip coming this summer -- 07/07/2014 by Brad Linder”。2014年的VIA的2GHz的Isaiah II QuadCore處理器的性能基本和AMD Kabini的Athlon 5350和Intel Atom的Z3770相當,詳細參數見圖11。

(圖11)

以下為鏈接:

根據2015年的一篇文章,“VIA’s New 28nm C4650 QuadCore x86 Processor Spotted – Gaming and General Purpose Benchmarks Surface, Impressive Low-End Performance”。從中可以推測在至少在2015年,VIA已經有了VIA QuadCore C4650。以下為鏈接:

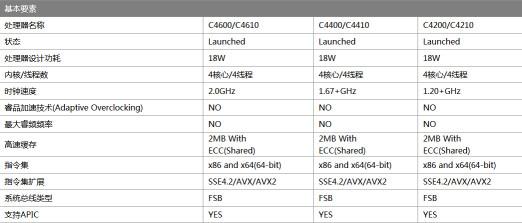

在2016年,兆芯宣布開始將量產100萬套ZX-C四核X86處理器。這里先介紹下C4600和ZX-C的關系。根據兆芯官網資料,ZX-C可分為C4200/4210、C4400/4410、C4600/C4610三個類別,之間的差別在于主頻,C4600是ZX-C系列處理器的2.0G主頻版本,兆芯官方截圖見圖12和圖13。

(圖12)

(圖13)

而且之前已經介紹了,從C4600芯片cpuinfo的信息可以看出,C4600的設計廠商(vendor_id)還是VIA的Centaur公司,而沒有改為ZX的標志。

兆芯的C4600與VIA公司的QuadCore C4650有非常緊密的聯系。這種聯系存在兩種可能:

第一種可能是,Centaur公司已經由威盛公司完全出售給了兆芯公司了,所以直接使用Centaur公司的標志,Centaur公司的技術成果也就順理成章的成為國家“十二五”核高基重大科技專項創新成果。

第二種可能是,通過VIA的關系,兆芯直接把QuadCore C4650的設計或版圖買過來,或者直接拿過來,重新在臺積電流片,然后改頭換面變成了國家“十二五”核高基重大科技專項創新成果。

以賽亞和以賽亞2到底有多少差異

根據資料顯示:兆芯ZX-A處理器,如C4350AL的微結構是“以賽亞”,而ZX-C系列處理器,比如C4600的微結構是“以賽亞2”。那么,以賽亞和以賽亞2到底有多少差異呢?

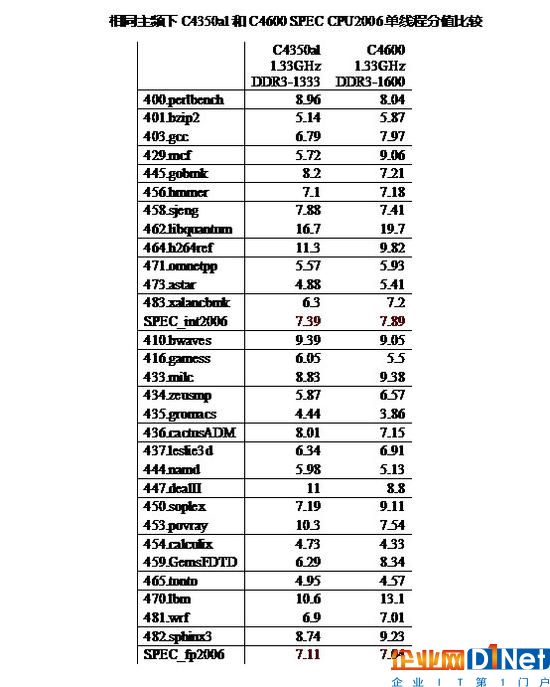

下面對VIA Nano X2 C4350AL和兆芯C4600在進行測試。實驗中為了盡可能較少不同的因素,將C4600和C4350al的頻率都降到1.33GHz。不過,受條件有限的原因,還是有一些區別的——C4600使用內存為DDR3-1600,C4350al使用的內存為DDR3-1333,C4600編譯選項最高采用SSE4.2,而C4350al編譯選項最高支持到SSE4.1,另外,兩個平臺的前端總線(FSB)頻率也不同,C4600為1333MHz,C4350al為1066MHz。

(圖14)

從圖14的對比可以看出,在相同主頻下,C4600和C4350al的SEPC2006的分值基本相當,也就是兩者在相同頻率下的性能基本相同。拋開主頻的影響和編譯器的影響,處理器性能的差別在于微結構的差別。

由于即便是同一款處理器跑兩次SEPC2006的分值也有有少許上下浮動。因而可以推斷出兆芯的C款處理器C4600和兆芯的A款處理器VIA Nano C4350AL采用了相同的微架構,或者說以賽亞和以賽亞2的差異微乎其微,以至于在性能上處于原地踏步狀態。

除了前端總線的頻率和工藝的差別,各種微結構的參數都沒有任何變化,也就是說“以賽亞2”和“以賽亞”其實是同一個東西,或者說修改的地方微乎其微,以至于在性能上處于原地踏步狀態,修改可以忽略不計。

必須說明是是實驗中,C4600的定點性能比C4350al略高一些,主要原因是C4600的前端總線的頻率提高了,C4600浮點性能反而略有下降,主要原因是由于其采用的SSE4.2指令集沒有硬件的邏輯實現,并且DDR3-1600帶寬的提升反而彌補不了延遲的略微增加,以至于浮點性能下降。

兆芯C4600和VIA以賽亞的短板

Centaur公司設計的以賽亞在當時是立足差異化競爭的產物,以賽亞也是一個輕量級的架子,雖然在2009年的時候這個設計還是挺不錯的。但隨著技術的進步,以賽亞在今天就有點不夠看了,面對ARM Cortex A57/A72/A73就難以招架了。下面簡單介紹一下兆芯C4600和VIA以賽亞的短板:

短板一:沒有對最新的指令系統在微結構和硬件上進行改動

根據VIA官方資料,VIA Nano只支持到SSE4.1指令集系統,至于原因只要回溯Intel指令集系統的發展歷史就明了了:MMX(1996), SSE(1999), SSE2(2001), SSE3(2004),SSSE3(2006), SSE4.1(2006)SSE4.2(2007), AES, AVX(2011), F16C(2009), ACE, PCLMUL(2010), VMX, BMI1, BMI2, AVX2(2013)。

正是因為歷史原因以及Intel對外的X86授權因素,當時的VIA公司沒有拿到Intel最新指令集系統的授權,所以2009年的Nano處理器最高支持到SSE4.1。

相比之下,VIA QuadCore C4650和兆芯C4600處理器支持后續的SSE4.2和最新的AVX和AVX2等指令集系統。

對于VIA QuadCore C4650和兆芯C4600支持最新的AVX和AVX2等指令集系統,可能的原因是VIA已經買到了Intel公司最新指令集系統的授權。不過VIA如何將指令集授權轉讓給兆芯,這個問題無論是Intel,還是VIA、兆芯都沒有任何公開聲明。

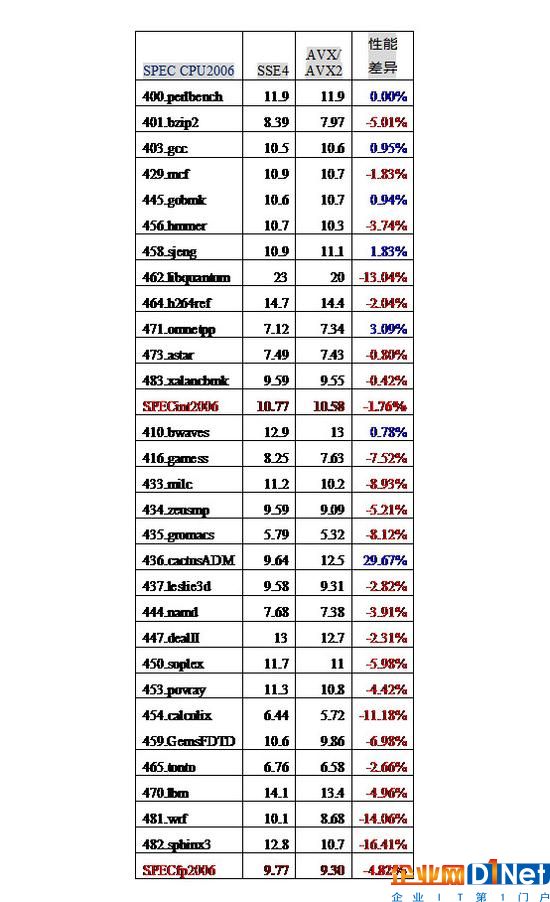

誠然,這個不是本文關注的重點。本文關注的是緣何增加了AVX和AVX2等指令集系統C4600的性能反而下降了。

Intel和AMD的CPU在使用了最新的256位的AVX/AVX2向量指令集后,性能有所提高——Intel和AMD處理器采用向量指令(128位和256位),INT2006的性能平均可以提高5%,FP2006的性能平均可以提高16-18%。而從128位的SSE,增加到256位的AVX/AVX2指令,INT2006的性能可以提高2-3%,FP2006的性能可以提高6-8%。

必須說明的是,采用向量指令提高性能的前提是處理器的訪存通路能供應上足夠寬的數據,如Haswell為了支持256位的AVX/AVX,采用了3個訪存的端口,同時支持2個256位的load操作和1個256位的store操作。

與Intel和AMD的CPU相反,C4600處理器兼容了Intel最新的256位向量指令AVX/AVX2等(不支持乘加FMA指令)。在編譯時打開了AVX2, AVX, bmi等最新指令集編譯選項,但編譯出來的程序實測性能反而下降。具體成績為圖15。

(圖15)

從圖15中可以看出,采用最新的指令集系統,對于大部分CPU2006的程序,其性能反而下降了。對于INT2006,幾何平均的性能下降了1.76%,如401.bzip2下降了5.01%,456.hmmer下降了3.74%,462.libquantum下降了13.04%;對于FP2006,幾何平均的性能下降了4.82%。416.games下降了7.52%,433.milc下降了8.93%,435.gromacs下降了8.12%,454.calculix下降了11.18%,454.calculix下降了14.06%,459.GemsFDTD下降了6.98%,482.sphinx3下降了16.41%。而這些程序正好是易于被向量化的程序,其采用了256位的AVX指令。例如459.GemsFDTD中256位的Packed Double動態指令數占到16.53%。

為什么采用新型的指令集系統,SPEC CPU2006程序性能反而有所下降呢?很可能是兆芯C4600處理器保留了Centaur公司的原始設計,沒有對最新的指令系統在微結構和硬件上進行改動,也就是在微結構上除了指令譯碼部分,在數據通路和訪存通路上沒有變化。而這也作證了之前提到的:以賽亞2和以賽亞其實是同一個東西,或者說修改的地方微乎其微。

首先來看處理器在指令譯碼部分怎么支持最新的指令集系統,在當前的CISC指令集系統的實現都是將外部CISC指令翻譯為內部的類RISC,即uops,通常一條CISC指令可以在內部被翻譯為1-3條內部的uops指令。uops指令在“以賽亞”被稱為micro-ops,見VIA Isaiah Architectural文章中“microcode subsystem”,“以賽亞”架構中的微碼子系統(microcode subsystem)包括24K微指令加上一個強大的打補丁(patch)的功能,使得微碼能被更新,每個ROM中的微碼指令被翻譯為最多3條融合的微操作(fused micro-ops)。可以看出“以賽亞”架構仍然在沿用X86處理器早期的部分復雜X86指令微碼實現的方式,如果要支持新的如AVX的指令,就可以通過更新微碼的方式來實現,再通過微碼指令轉換為內部的微操作指令實現。

第二,256位寄存器的實現,既然要支持AVX指令,需要實現256位的體系結構可見的寄存器和256位的重命名物理寄存器,我們猜測其內部實現為僅實現了體系結構可見的寄存器,而沒有實現256位的重命名物理寄存器,這不會增加太多的開銷。在數據通路和訪存通路的實現上,在內部很可能是將256位的向量指令拆分為多條128位的類SSE指令實現的,這種方法在第一代AMD的推土機實現256位的AVX指令和第一代的K8實現128位的SSE指令也是這么做的,通過內部拆分在數據通路上支持新的指令集系統,但是這樣做的結果是,新的指令系統對性能不但沒有好處,反而會有性能的下降,因為數據通路和訪存通路根本就沒有實現更寬的設計,就好比本身很窄的馬路,可以通過2個車道,這時候同時來4輛車,這4輛車就得排成兩排,順序通過。另外,更寬的向量操作導致其架構的訪存和供數能力跟不上,這也造成了新指令集有時性能下降的原因。

短板二:前端總線設計和帶寬

限制兆芯C4600芯片的一大瓶頸是Centaur公司延續了其前端總線(VIA V4 bus)的設計,而且沒有將內存控制器集成到處理器上。

前端總線(front-side bus,FSB)是早期Intel芯片的計算機通信的接口,和AMD公司的EV6類似,其連接CPU和北橋芯片,內存控制器通常集成在北橋中。PCI,AGP等各種設備以及內存都是通過北橋和CPU進行通訊。

前端總線出現在1995-2006,用于Intel的Atom,Celeron,Pentium,Core2芯片以及早期的Xeon芯片,其很快被現代處理器中AMD的HT(HyperTransport)和Intel的QPI(QuickPath Interconnect)以及DMI(Direct Media Interface)所取代。

前端總線為64位,8個字節,每拍能傳輸4次。前端總線的速度是當時計算機系統一個重要的衡量指標,當前,前端總線最高的頻率為333~400MHz,每個周期能進行4次傳輸。由于設計的缺陷,前端總線的頻率沒法得到進一步提升。假設前端總線的實際頻率為333MHz,也就是通常廠家說的1333MHz,其峰值理論帶寬為10.65GB/s,即8 bytes/transfer × 333 MHz × 4 transfers/cycle = 10656MB/s。

前端總線的設計,使得CPU需要等待來自內存中的數據,對于每個元素需要的大量復雜計算的應用,這樣的應用訪存不是那么的密集,前端總線能跟上CPU的速度。而對于圖像、音頻、視頻、游戲、FPGA綜合以及科學應用等應用,通常是對于大工作集的少部分數據進行操作,這樣前端總線就成為一個主要的性能瓶頸。

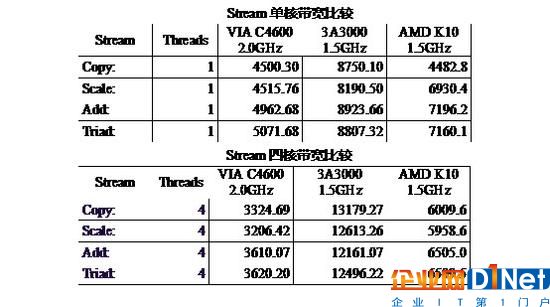

圖16比較了2.0GHz的兆芯C4600、1.5GHz的龍芯3A3000、1.5GHz的AMD K10三款處理器訪存帶寬測試程序STREAM的帶寬分值,從中可以看出,單線程STREAM的測試,C4600的STREAM帶寬基本為4-5GB/s,而3A3000為8+GB/s,K10為6-7GB/s。多線程STREAM的測試,C4600的STREAM帶寬基本為3+GB/s,而3A3000為12-13GB/s,K10位6+GB/s。

(圖16)

國際主流CPU都在十年前把內存控制器集成在CPU芯片中,而兆芯C4600繼續把內存控制器集成在橋片上,訪存帶寬受限于前端總線。VIA 以賽亞系列處理器從2009年開始一直采用VIA V4 BUS的前端總線設計,而沒有將內存控制器集成到芯片上,即使是2014年對Nano X2的改版也不愿意去動其結構和設計。只是從40nm工藝提高到28nm TSMC的工藝,同時把V4總線的頻率從800MHZ提高到1333MHz,也就是其前端總線的理論帶寬為10.6GB/s。所以其內存帶寬不高原因也就可以解釋。

另外,多線程的情況下,多個CPU核以及I/O等會競爭前端總線,前端總線和內存控制器的預期機制截然不同,造成訪存序的紊亂。所以在多個線程尤其是訪存壓力很大的情況下,其性能會急劇下降。這也是C4600多線程帶寬反而不如單線程帶寬的原因。

對于C4600,1-2個核基本上就吃滿了訪存帶寬,對于龍芯3A3000而言,訪存帶寬具備顯著的優勢,其能滿足4-8個處理器核的需求。所以,在單線程性能差距不大的情形下,龍芯3A3000的SPEC CPU2006多線程rate的性能,明顯超過了C4600的rate性能。具體參數見圖17

(圖17)

結語

雖然在一系列兆芯官方宣傳和中文宣傳資料上,兆芯一直宣傳自主安全可控(見圖18),在其官方網站上也標明自主可控(見圖19)。但與兆芯相關的英文材料卻標明:Based on Centaur Technologie’s microarchitecture designs (見圖20)。

(圖18)

(圖19)

(圖20)

在微結構源自Centaur公司,指令集授權也模糊不清的情況下,就宣布兆芯自主安全可控,未免有點超之過急——即便是走技術引進道路,也要在憑借自己的能力完成消化吸收再創新之后,才能稱得上自主可控安全。比如在充分消化Centaur公司設計的以賽亞之后,憑借境內設計團隊設計出可以匹敵Intel SNB或者AMD Zen的產品,這才真的稱得上再創新。拿Centaur公司設計的以賽亞,改制程堆核心數提升總線頻率做出一款CPU就宣傳自主可控,無非是自欺欺人而已。

至于拿Centaur公司早年的設計,改頭換面就成為國家“十二五”核高基重大科技專項創新成果,并能夠榮獲“第18屆中國國際工業博覽會金獎”(見圖21)、“2017年度大中華IC設計成就獎”(見圖22)、“第十一屆(2016年度)中國半導體創新產品和技術獎”(見圖23),也難怪國外資深IC設計工程師會對中國的IC設計水平嗤之以鼻了。

(圖21)

(圖22)

京公網安備 11010502049343號

京公網安備 11010502049343號