Intel今天在北京精尖制造日上展示了從22nm到3nm等各種先進(jìn)工藝,并直言臺積電、三星的所謂10nm只有自己14nm的水平,如此公開叫板實屬罕見。

當(dāng)然,最關(guān)鍵的還是10nm,大家都在等待今年底或明年初Cannon Lake的誕生,不過Intel此前曾表示,其第一款10nm產(chǎn)品將面向數(shù)據(jù)中心市場。

要知道,Intel Xeon至強(qiáng)處理器都是同一家族中排在消費級后邊才發(fā)布的,這次難道要提前?

非也。Intel這里說的首款10nm工藝數(shù)據(jù)中心產(chǎn)品,指的其實是FPGA(現(xiàn)場可編程門陣列),Intel下一代FPGA就將應(yīng)用10nm工藝,代號為“Falcon Mesa”。

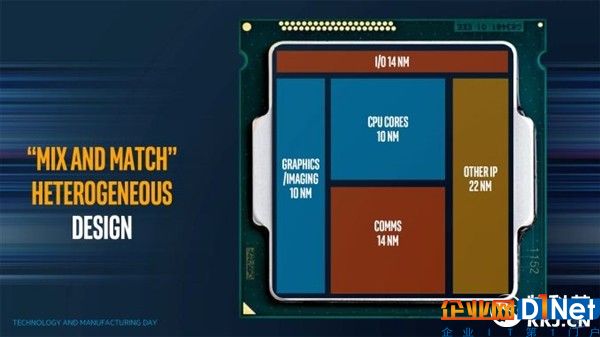

Falcon Mesa最特殊的地方不是搶先用新工藝,而是在同一顆芯片封裝內(nèi),使用不同工藝!

Intel將這種不同工藝混合搭配的技術(shù)稱為Mix and Match異構(gòu)設(shè)計,簡單地說就是將不同工藝制造的不同模塊,統(tǒng)一封裝在同一個基底上,比如說CPU、GPU核心用10nm,IO和通信模塊用14nm,其他IP模塊則是22nm。

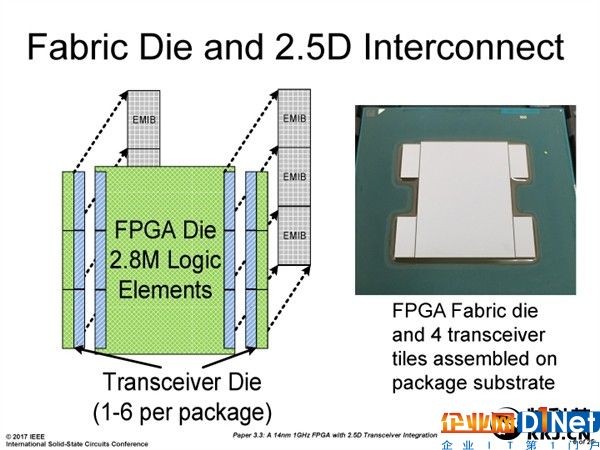

不同模塊之間使用Intel第二代嵌入式多內(nèi)核互連橋接(EMIB)封裝技術(shù)連在一起,可提供112Gbps的串行通道,或者PCI-E 4.0 x16通道,所以帶寬和延遲都不是問題。

甚至,Intel未來也會使用HBM高帶寬內(nèi)存。

Intel今年展示的一個樣品,就在FPGA內(nèi)核的旁邊,放置了四個單獨的收發(fā)器模塊,挺像AMD Fiji/Vega GPU旁邊放著HBM顯存,但是Intel沒有披露具體都是什么工藝。

為什么要用這種“膠水”設(shè)計呢?最大好處還是靈活,可以根據(jù)需要隨時添加、刪減各種模塊,滿足不同客戶和應(yīng)用需求,而且每一種模塊可以使用最合適的工藝制造,而不必用同一種工藝做出一個巨大的芯片。

AMD EPYC/Ryzen ThreadRipper處理器今年就用了多Die封裝設(shè)計,官方解釋原因就是可以大大提高良品率,降低成本。

看樣子,F(xiàn)alcon Meda會在今年底之前發(fā)布。

京公網(wǎng)安備 11010502049343號

京公網(wǎng)安備 11010502049343號