本周Centriq 2400設計藍圖將正式發布。

高通公司數據中心芯片部門負責人Anand Chandrasekher手持Centriq芯片

高通公司曾將來自其旗艦級驍龍芯片(被數以百萬計智能手機與平板設備所使用)開發團隊的工程師們調往其剛剛起步的數據中心處理器Centriq芯片部門。

這種關注重點的轉化意味著高通公司開始將注意力集中在服務器領域,而就在今天(星期二)晚,相關成果終將亮相——Centriq內部設計方案將在本屆于硅谷召開的Hot Chips大會上公開。

將眾多原本隸屬驍龍部門的工程師重新調往Centriq可能恰好解釋了為何高通公司決定將內部設計的移動Kryo核心替換為現成ARM Cortex核心——或者是經過輕微調整的版本。事實上,高通公司已經停止了全面定制化Kryo芯片的開發工作。

當然,仍有一部分移動CPU設計師繼續留在驍龍研發團隊當中,而且工程師們亦可根據需求隨時被調回。根據我們掌握的情況,目前移動開發組仍然擁有充足的人手,能夠繼續推動驍龍芯片家族的順利發展。這部分消息已經得到了高通公司多位高管的證實。

去年年末,高通公司發布了驍龍835,這款高性能系統級芯片將從今年開始由頂級Android智能手機過渡到Windows 10筆記本當中。這款處理器并未采用內部開發的Kryo核心,而是選擇了經過輕松調整的現成CPU計算核心——很可能是四Coretex-A53加四A72或者A73的組合,且由ARM公司提供授權。高通方面將其稱為“半定制”與“構建在ARM Cortex技術之上”的方案。

今年5月,高通公司面向智能手機發布了更為高端的驍龍處理器:660與630。然而,其中660采用了來自驍經820系列的八個Kryo核心,而630則采用八個ARM Cortex-A53核心。

這并不是說ARM公司的現成核心就不好。只是這種轉變意味著高通公司的其它設計方案——包括其GPU、DSP、機器學習功能以及調制解調器——必須得想辦法讓其移動系統芯片煥發出獨特的光彩,從而在與其它同樣采用現成Cortex核心的廠商當中脫穎而出。這對于高通公司無疑是重要的一步,特別是考慮到其核心業務正是移動處理器與無線調制解調器芯片組。

值得一提的是,高通公司管理層表示,他們的想法是在正確的時間在移動端采用正確的計算核心——這意味著現成Cortex CPU在表現上顯然優于高通內部設計的驍龍CPU。

轉向數據中心領域

本周二晚上,Centriq 2400設計藍圖將由高通公司高層人士在本屆于加利福尼亞州庫比蒂諾召開的Hot Chips大會上向芯片工程師與計算機科學家們展示。我們此前曾經介紹過這款采用10納米制程的ARMv8處理器產品線。高通公司曾在本周強調稱,盡管設計人員來自驍龍處理器團隊,但Centriq從設計之初就專門面向云計算與服務器工作負載等場景。

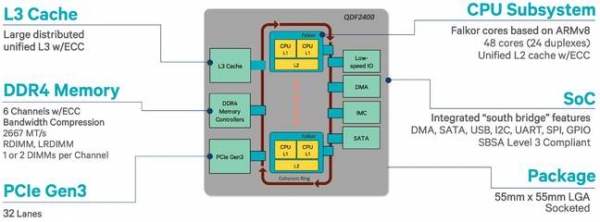

Centriq原理圖

在這方面,很多朋友可能會對高通公司食言而肥的作法有所抱怨。在我們于上周看到的Hot Chips演示文稿當中,該公司表示Centriq處理器采用“第五代定制化核心設計”,旨在“從根本上滿足云服務供應商的實際需求”。

Centriq產品管理高級主管Chris Bergen解釋稱,這意味著現有工程師團隊,包括來自驍龍處理器開發組的成員,正在努力進行其第五代定制化CPU設計,且將從零開始打造出一款服務器友好型系統芯片。

然而著眼于藍圖本身,可以肯定的是這絕不是一款加大版的智能手機CPU。

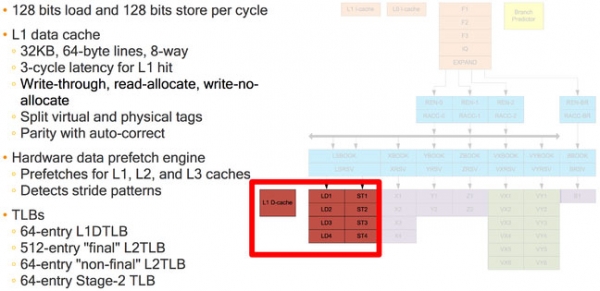

這款代號為Falkor的處理器擁有48個計算核心,且僅能運行64位ARMv8代碼。其并不提供32位模式。這款系統芯片支持ARM的虛擬機管理程序權限等級(簡稱EL2),可提供一套TrustZone(EL3)環境,且以可選方式包含AES、SHA1以及SHA2-256等加密算法的硬件加速能力。各計算核心被部署在一條環狀總線之上,類似于英特爾剛剛停止在其至強處理器上使用的設計思路。芯片巨頭并不喜歡以環狀結構提升其芯片內的計算核心數量,轉而選擇了網狀柵極——但高通方面則明顯更喜歡這種快速雙向頻段思路。

其共享三級緩存被附加在環狀結構當中,且看起來均勻分布在各計算核心之間。根據我們得到的消息,該環狀互連結構的總傳輸帶寬至少可達每秒250 GB。另外,據稱這一環狀結構還進行了分段,我們認為這代表著其中可能包含復數個環。因此,總計48個計算核心當中可能有24個處于一套環內,而另外24個核心則處于另一套環中,并由各環狀體系將其對接在一起。

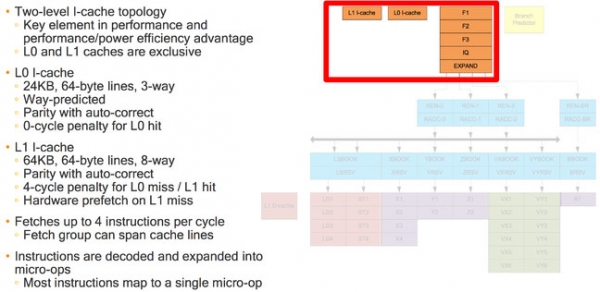

說到高速緩存,高通公司今年之內應該會實現這款芯片的量產,但并不會對緩存大小進行提升。每個計算核心擁有一個24 KB的64字節行零級指令緩存,一個64 KB 64字節行一級I-緩存,外加32KB一級數據緩存。其余的二級與三級緩存大小目前仍不明確。這款芯片目前僅提供樣品,因此大家只能立足主流服務器芯片制造商英特爾公司的現有設計方案進行研究。高通公司顯然不希望過早披露關鍵信息導致英特爾方面有所防備。

一級與零級緩存

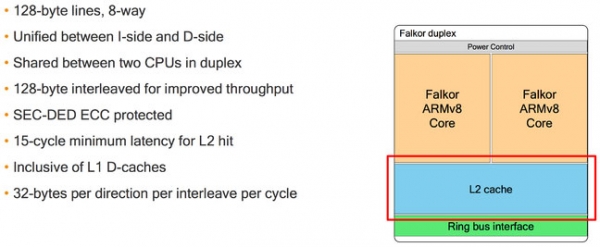

其中零級緩存尤其值得關注:其作為一級I-緩存的擴展充當指令獲取緩沖區。換句話來說,其很像是那種典型的前端緩沖區,每個周期會消耗四條指令,但具體作用則與緩存完全相同:例如,CPU可對其進行無效化與刷新。二級緩存則負責容納數據與指令,且可實現128字節行八路運行,一次命中的最低延遲為15個周期。

二級緩存

三級緩存擁有一項服務質量功能,允許各虛擬機管理程序與內核對虛擬機以及線程進行組織,以便確保擁有較高優先級的虛擬機能夠占用較其它虛擬機更高的緩存容量。該芯片亦可實現實時內存壓縮,延遲為2到4個周期,且面向軟件開放。根據我們得到的消息,128字節行可被壓縮為64字節行,并在可能的情況下進行糾錯。

當高通公司提到48個計算核心時,最終產品一定就是48個計算核心——不存在任何超線程或者其它類似的縮水作法。Falkor芯片可對共享的二級緩存進行配對以實現雙工傳輸。每個計算核心皆可開啟與關閉,具體取決于工作負載需求——相當于由輕度睡眠(CPU時鐘關閉)到全速運轉。其提供32條PCIe通道,6條DDR4內存通道并配合有糾錯功能。每通道擁有1到2個DIMM,外加SATA、USB、串行與通用IO接口。

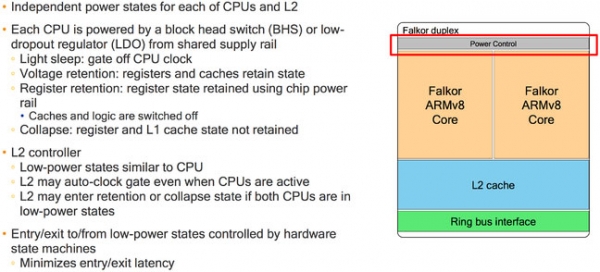

功耗控制

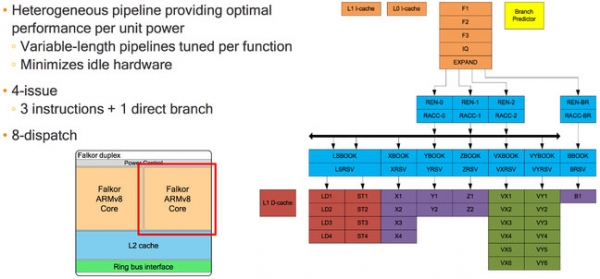

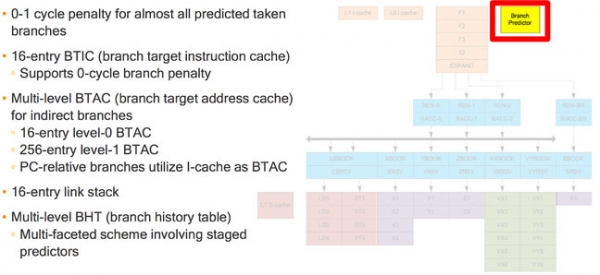

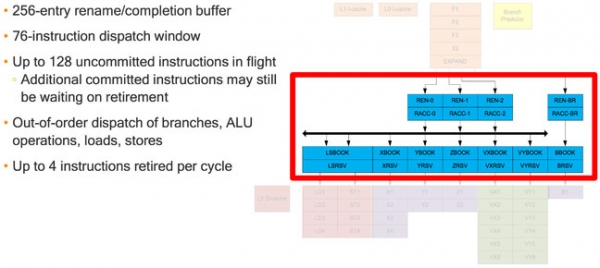

更進一步挖掘,可以發現其擁有可變長度管道,意味著可在每周期內最多發出三條指令外加一條直接分支。另外,其還擁有8條調度通道。其可實現無序執行,并對資源進行重命名。每個預測分支擁有一個0或1懲罰評分,一套16入口分支目標指令緩存,外加一套三級分支目標地址緩存。

Centriq的管道結構

分支預測器

管道隊列

管道的負載存儲分段

可變長度整數處理部分

這款芯片搭載有不可變片上ROM,其中包含一款啟動加載程序,可用于驗證通常被保存在閃存內的外部固件,同時確保僅運行合法代碼。處理器內的安全控制器可容納來自主通、服務器制造商以及客戶的軟件驗證用加密公鑰。因此,設備將僅在未從ROM或者早期啟動加載程序中發現漏洞的前提下啟動可信代碼并構建信息來源。

在本周召開的Hot Chips大會上,我們將持續為大家帶來更多新鮮出爐的重要消息。另外,當相關價格、緩存大小與其它信息得到披露之后,我們還將發文將至強、Centriq與Epyc進行一番規格比較。

京公網安備 11010502049343號

京公網安備 11010502049343號