微納電子系博士生涂鋒斌在大會上作學術報告

國際計算機體系結構大會是計算機體系結構領域的頂級會議。本次大會共收到378篇投稿,收錄64篇論文,涂鋒斌報告的研究論文是今年大會中國唯一被收錄的署名第一完成單位的論文。清華大學微納電子系尹首一副教授為本文通訊作者,涂鋒斌為本文第一作者,論文合作者還包括清華大學微納電子系魏少軍教授和劉雷波教授。

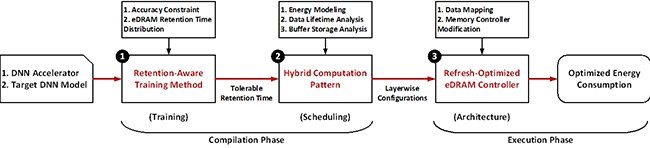

隨著人工智能應用中神經網絡規模的不斷增大,計算芯片的大量片外訪存會造成巨大的系統能耗,因此存儲優化是人工智能計算芯片設計中必須解決的一個核心問題。可重構研究團隊提出一種面向神經網絡的新型加速框架:數據生存時間感知的神經網絡加速框架(RANA)。RANA框架采用了三個層次的優化技術:數據生存時間感知的訓練方法,混合計算模式和支持刷新優化的增強動態隨機存取存儲器(eDRAM)存儲器,分別從訓練、調度和架構三個層面優化整體系統能耗。實驗結果顯示,RANA框架可以消除99.7%的eDRAM刷新能耗開銷,而性能和精度損失可以忽略不計。相比于傳統的采用SRAM的人工智能計算芯片,使用RANA框架的基于eDRAM的計算芯片在面積開銷相同的情況下可以減少41.7%的片外訪存和66.2%的系統能耗,使人工智能系統的能量效率獲得大幅提高。

數據生存時間感知的神經網絡加速框架(RANA)

微納電子系可重構計算團隊近年來基于可重構架構設計了Thinker系列人工智能計算芯片(Thinker I,Thinker II,Thinker S),受到學術界和工業界的廣泛關注。可重構計算團隊此次研究成果,從存儲優化和軟硬件協同設計的角度大幅提升了芯片能量效率, 為人工智能計算芯片的架構演進開拓了新方向。

京公網安備 11010502049343號

京公網安備 11010502049343號