近日,《華強電子》記者在采訪Achronix市場營銷副總裁Steve Mensor時獲悉,其第四代新的Speedcore Gen4 eFPGA架構已經推出,采用臺積電7nm工藝節點,主要針對新興人工智能/機器學習和高數據帶寬應用的爆炸式需求,將于2019年上半年投入量產。

Steve表示:“Speedcore IP是可以集成到ASIC和SoC之中的嵌入式FPGA(eFPGA)。客戶通過定制其邏輯、RAM和DSP資源需求,Achronix接下來就會為其配置滿足其需求的Speedcore IP,Speedcore查找表(LUT)、RAM單元模塊和DSP64單元模塊可以像樂高積木一樣進行組合,以便為特定的應用創建優化的可編程功能。在Speedcore IP的交付包中,也包括一個對Speedcore IP進行編程的ACE設計工具個性化版本。與之前一代的Speedcore 嵌入式FPGA(eFPGA)產品相比,Speedcore Gen4的性能提速60%、功耗降低50%、芯片面積縮小65%;新的機器學習處理器(MLP)單元模塊為人工智能/機器學習(AI / ML)應用提供高出300%的性能。”接下來Steve為記者詳細介紹了Speedcore Gen4新架構主要通過哪些創新來實現能效的顯著提升的。

架構性創新是提高系統性能的核心

與上一代Speedcore產品相比,新的Speedcore Gen4架構采用7nm工藝制程,在邏輯單元模塊中的布線布局、矩陣乘法、查找表等方面實現了多項創新,從而可將系統整體性能提高60%。

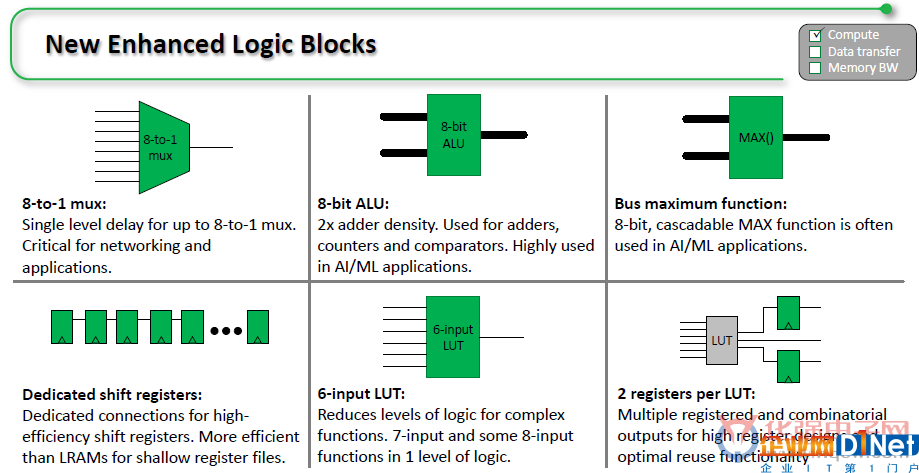

新增強的邏輯模塊

其中的路由架構也借由一種獨立的專用總線路由結構得到了增強。新的總線路由是高性能專用總線分組路由通道,總線路由與標準路由通道分離,以確保無擁塞。在內存和MLP之間運行的總線優化,創建巨型分布式運行時可配置交換網絡。這為高帶寬和低延遲應用提供了最佳的解決方案,并在業界首次實現了將網絡優化應用于FPGA互連。

高速核心下一代布線架構

矩陣向量乘法將行劃分成塊,大型矩陣通常將與矩陣的一行相關聯的單個乘積和劃分成多個循環。例如: 將32個乘積的和分為8個乘積的四個部分和,累積四個連續的部分和,以計算每行的積的總和。第一個輸出的總和在第四個時鐘周期結束時完成。對接下來的四個時鐘周期進行相同的處理,以計算和組合與第二輸出相關聯的四個部分和。

基于循環寄存器的塊矩陣矢量乘法,循環寄存器允許向量數據被存儲和重用。在并行操作中顯示多個MAC操作的例子,讀取矢量的四個子塊并將數據寫入循環寄存器文件。

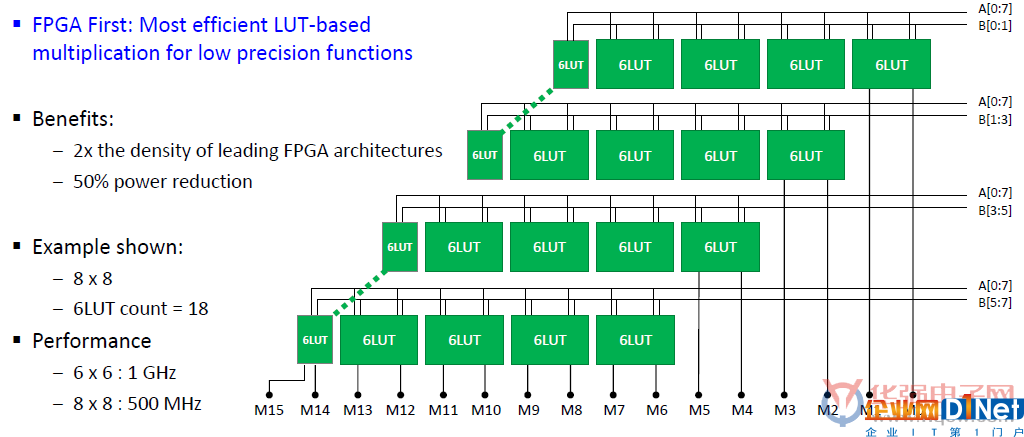

其中查找表的所有方面都得到了增強,以支持使用最少的資源來實現各種功能,從而可縮減面積和功耗并提高性能。其中的更改包括將ALU的大小加倍、將每個LUT的寄存器數量加倍、支持7位函數和一些8位函數、以及為移位寄存器提供的專用高速連接。使用LUTS構建附加乘法器,使得有價值的低精度乘法通過最有效的FPGA來實現。

基于GE4LUT的乘法器:比其他FPGA架構更有效

另外,核心架構的研發創新同時能滿足多種工具的支持也是非常重要的。Achronix的ACE設計工具中包括了Speedcore Gen4 eFPGAs的預先配置示例實例,它們可支持客戶針對性能、資源使用率和編譯時間去評估Speedcore Gen4的結果質量;Achronix現已可提供支持Speedcore Gen4的ACE設計工具。Speedcore采用了一種模塊化的架構,它可根據客戶的要求輕松配置其大小。Achronix使用其Speedcore Builder工具來即刻創建新的Speedcore實例,以便滿足客戶對其快速評估的要求。

最佳的人工智能/機器學習加速器

正是基于以上新架構的技術,使得Speedcore Gen4對人工智能/機器學習應用的高密度和針對性計算產生了顯著增加的需求。與以前的Achronix FPGA產品相比,新的Achronix機器學習處理器(MLP)利用了人工智能/機器學習處理的特定屬性,并將這些應用的性能提高了300%。這是通過多種架構性創新來實現的,這些創新可以同時提高每個時鐘周期的性能和操作次數。

新的Achronix機器學習處理器(MLP)是一個完整的人工智能/機器學習計算引擎,支持定點和多個浮點數格式和精度。每個機器學習處理器包括一個循環寄存器文件(Cyclical Register File),它用來存儲重用的權重或數據。各個機器學習處理器與相鄰的機器學習處理器單元模塊和更大的存儲單元模塊緊密耦合,以提供最高的處理性能、每秒最高的操作次數和最低的功率分集。這些機器學習處理器支持各種定點和浮點格式,包括Bfloat16、16位、半精度、24位和單元塊浮點。用戶可以通過為其應用選擇最佳精度來實現精度和性能的均衡。

為了補充機器學習處理器并提高人工智能/機器學習的計算密度,Speedcore Gen4查找表(LUT)可以實現比任何獨立FPGA芯片產品高出兩倍的乘法器。領先的獨立FPGA芯片在21個查找表可以中實現6x6乘法器,而Speedcore Gen4僅需在11個LUT中就可實現相同的功能,并可在1 GHz的速率上工作。

解決帶寬爆炸問題 目標市場的現在與未來

那么采用臺積電7nm工藝節點的Speedcore Gen4,主要針對新興人工智能/機器學習和高數據帶寬應用的爆炸式需求外,還有哪些目標市場呢?Steve向《華強電子》表示,計算加速度,網絡加速,5G基礎設施, 智能駕駛這些都是他們的目標市場。這些應用程序具有相同的要求:高性能、低功耗、低延遲、可編程硬件加速器。過去幾年,存儲和網絡主導了FPGA用戶群,但未來幾年,計算端的需求將遠遠超過存儲和網絡,并都將沿著穩定的增長線繼續發展,在機器學習,高性能計算,數據分析等領域,FPGA將更有用武之地。Steve尤其看好網絡加速和5G市場的應用前景,比如在5G基礎設施方面的壓縮/減壓,非結構化數據匹配 ,數據庫加速,適應前沿標準的協議適應性,基帶和分裂L1加速,基于人工智能的波束形成,放大器預失真,移動邊緣計算這些細分市場都對高性能FPGA有著強烈的需求。

在網絡加速方面,固定和無線網絡帶寬的急劇增加,加上處理能力向邊緣等進行重新分配,以及數十億物聯網設備的出現,將給傳統網絡和計算基礎設施帶來壓力。這種新的處理范式意味著每秒將有數十億到數萬億次的運算。傳統云和企業數據中心計算資源和通信基礎設施無法跟上數據速率的指數級增長、快速變化的安全協議、以及許多新的網絡和連接要求。傳統的多核CPU和SoC無法在沒有輔助的情況下獨立滿足這些要求,因而它們需要硬件加速器,通常是可重新編程的硬件加速器,用來預處理和卸載計算,以便提高系統的整體計算性能。經過優化后的Speedcore Gen4 eFPGA已經可以滿足這些應用需求。

另外,對于FGPA成本這個問題,Steve也給出了肯定的答復,采用新架構新工藝的最新Speedcore eFPGA IP,和上一代產品基本持平,不會增加用戶成本。對于已量產的Speedcore架構,Achronix可在6周內為客戶配置并提供Speedcore eFPGA IP和支持文件。采用臺積電7nm工藝節點的Speedcore Gen4將于2019年上半年投入量產,Achronix還將于2019年下半年提供用于臺積電16nm和12nm工藝節點的Speedcore Gen4 eFPGA IP。

但Speedcore Gen4已經有市場實例,Micron日前推出GDDR6存儲器就是采用Achronix臺積電7nm工藝技術的FPGA芯片,實現了高達16 Gb / s的吞吐量。GDDR6針對包括機器學習等諸多要求嚴苛的應用進行了優化,這些應用需要數萬兆比特(multi-terabit)存儲寬帶,從而使Achronix在提供FPGA方案時,其成本能夠比其他使用可比存儲解決方案的FPGA低出一半。

京公網安備 11010502049343號

京公網安備 11010502049343號