SLC的固態盤在如今的市面上已經是鳳毛麟角,MLC也越來越少,TLC開始成為市場的絕對主流。

1月15日,TheReg撰文,談到了QLC閃存的未來和3D NAND之間的關系,還是非常有趣的。

QLC顧名思義,就是4bits Cell,電信號存儲的密度更高。其實早在2009年,SanDisk(閃迪)就試圖用43nm工藝制造QLC閃存,但因為錯誤率奇高,不得不放棄。

錯誤率是Flash閃存一座不可避免的大山,通常的處理方式是主控中加入ECC校驗技術,即在數據位中插入校驗位。

說到這里你就明白了,數據位越少,出錯率必然越低,所以從存儲方式上,SLC必然是最扛用的,其次是MLC、QLC……

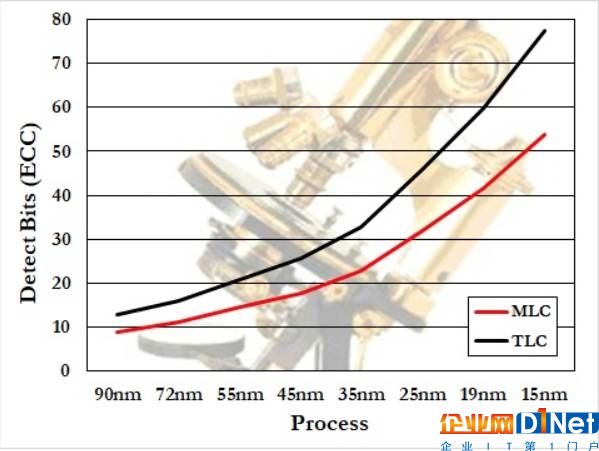

同時,工藝也是如此。制程越先進,ECC校驗位就要增多,糾錯難度就越高。

而閃迪之所以搞不定錯誤率這個問題是因為當時3D NAND還沒發展起來,基于43nm工藝的2D平面來做校驗,要想數據達到一定的準確率,要不容量很小,要不成品尺寸巨大。

而隨著3D NAND的成熟,TLC甚至QLC的未來突然豁然開朗起來。由于3D構造方式的優勢,浮柵周圍形成一圈作為支柱通道,面積增加3倍,所以30nm做出了90nm的效果,糾錯難度大大下降。

如圖所示,同樣是15nm級別,MLC閃存只需要50個ECC校驗位,而TLC則需要多達75個。

可在3D QLC閃存時代,20個ECC校驗位都綽綽有余。

Objective Analysis的專業人士Jim Handy撰文指出,所以,他說PLC閃存(5bits/Cell)是必然,因為一個最顯而易見的事實是,原來1TB QLC SSD立馬增大到1.25TB,屆時的1元1GB才會有可能。

京公網安備 11010502049343號

京公網安備 11010502049343號